# **Techniques for Testing Integrated Circuits**

# Thesis by

Erik P. DeBenedictis

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

California Institute of Technology

Pasadena, California

1983

submitted 5 May 1982

# **Acknowledgments**

Chuck Seitz and Carver Mead are the persons most deserving of acknowledgment. Chuck and Carver have worked closely with me on this testing research since 1979, giving me their ideas and making suggestions about mine. Chuck has also been very helpful in the preparation of this document, having given extensive suggestions about its technical and grammatical content.

Please let me express here my appreciation to the ARPA management both for their help in providing an environment whereby ideas can be shared among the university community, and for their support of this research. This research was supported by the Defense Advanced Research Projects Agency, ARPA Order number 3771, and monitored by the Office of Naval Research under contract number NO0014-79-C-0597.

# **Abstract**

A language is presented for describing tests of integrated circuits. The language has a high abstractive capability that enables test specifications to follow the structural or logical organization of a design. The test language is applied to a number of current design styles in a series of examples. Methods for designing integrated circuits for testability are demonstrated. An implementation of the test language through a test language interpreter and a tester is discussed. Tester designs are presented that will execute the test language with unusually high efficiency.

# Table of Contents

| 1.  | Introduction                                                            | 1                |

|-----|-------------------------------------------------------------------------|------------------|

|     | 1.1 A Tour Through the Design of an Integrated Circuit                  | 2                |

|     | 1.1.1 Initial Design and Testing                                        | 2<br>2<br>2<br>3 |

|     | 1.1.1.1 Description of the Pins                                         | 2                |

|     | 1,1,1,2 Initial Checkout                                                | 3                |

|     | 1.1.1.3 Common Errors                                                   | 5                |

|     | 1.1.2 Exhaustive Checkout                                               | 6                |

|     | 1.1.3 Testing an Adder as an Arithmetic Array                           | 8                |

|     | 1.1.4 Testing When Embedded in a System                                 | 9                |

|     | 1.1.4.1 Describing an Access Procedure                                  | 10               |

|     | 1.1.4.2 Testing a Part Through an Access Procedure                      | 11               |

|     | 1.2 Strategy for the Design of Tests and Design for Testability         | 13               |

|     | 1.2.1 Primitive Tests                                                   | 13               |

|     | 1.2.2 Application of Primitive Tests                                    | 13               |

|     | 1.2.3 Synergism of Testing and Design                                   | 14               |

|     | 1.2.4 Testability                                                       | 14               |

|     | 1.3 The Design of Testers                                               | 15               |

|     | 1.3.1 Test Generation Modes                                             | 15               |

|     | 1.3.2 Tester Construction for the Test Language                         | 17               |

|     | 1.3.3 Interface of the Test Language to Simulators                      | 17               |

|     | 1.4 The Value of an Interactive, Non-Embedded Test Language 1.4.1 ATLAS | 19               |

|     | 1.4.1 ATLAS 1.4.2 FACTOR                                                | 19               |

|     | 1.4.3 ANGEL                                                             | 20<br>20         |

|     | 1.4.4 The FIFI Test Language                                            | 21               |

|     | 1.5 Summary                                                             | 21               |

| 2   | A Notation for Describing Integrated Circuit Testing                    | 22               |

| Z • | 2.1 Abstract Elements of Digital Electrical Signals                     | 22               |

|     | 2.1.1 Elements of the Algebra                                           |                  |

|     | 2.1.1 Ports                                                             | 22               |

|     | 2.1.2 Ports 2.1.3 Equations and Assignments                             | 24<br>24         |

|     | 2.1.3.1 Assignments                                                     | 25<br>25         |

|     | 2.1.3.2 Expressions                                                     | 25               |

|     | 2.1.4 Specification of Analog Tests                                     | 28               |

|     | 2.2 Organization of Digital Manipulations into Test Matrices            | 28               |

|     | 2.2.1 A Restricted Test Language and Testing Efficiency                 | 29               |

|     | 2.2.2 Elements                                                          | 31               |

|     | 2.2.3 Test Matrices                                                     | 31               |

|     | 2.2.4 Static Interpretation                                             | 33               |

|     | 2.2.5 Dynamic Interpretation                                            | 35               |

|     | 2.3 Test Language Procedures                                            | 38               |

|     | 2.3.1 Procedure Defining and Calling Notations in Programming Languages | 39               |

|     | 2.3.2 Procedure Conventions in the Test Language                        | 39               |

|     | 2.3.3 Sophisticated Interpretation of the Interrogate Action            | 41               |

|     | 2.3.3.1 Simple Interpretation of the Interrogate Action                 | 42               |

|     | 2.3.3.2 A More Complex Interpretation of the Interrogate Action         | 42               |

|     | 2.3.4 Timing                                                            | 44               |

| 3. Examples of the Test Language                                                        | 46       |

|-----------------------------------------------------------------------------------------|----------|

| 3.1 Abstraction of a Bidirectional Data Bus                                             | 46       |

| 3.2 Performing Complex Data Manipulations                                               | 48       |

| 3.3 Testing a 16K Dynamic Random Access Memory                                          | 49       |

| 3.4 Multiphase Clocking and the Test Language                                           | 52       |

| 3.5 An Example of the Test Generation Technique for Large Systems                       | 55       |

| 3.5.1 Testing the Data Path Unit                                                        | 56       |

| 3.6 Testing the Data Fath offit 3.6 Testing a Microprogrammed System with a Data Path   | 58       |

| 3.6.1 Data Path Part                                                                    | 59       |

| 3.6.2 Microcode Part                                                                    | 61       |

| 3.6.3 State Latch Part                                                                  | 61       |

| 4. Testing of Sequential Systems                                                        | 63       |

| 4.1 Previous Approaches to Sequential Testing                                           | 63       |

| 4.1.1 Conventional Testing of Combinational Networks                                    | 64       |

| 4.1.2 New Methods for Testing Sequential Devices                                        | 65       |

| 4.1.3 LSSD                                                                              | 66       |

| 4.1.4 Testing Art                                                                       | 66       |

| 4.1.5 Other Methods                                                                     | 67       |

| 4.2 Structured Design and Design for Testability                                        | 68       |

| 4.2.1 The Value of Structured Design                                                    | 68       |

| 4.2.2 Structured Integrated Circuit Design                                              | 69       |

| 4.2.3 Testing Structured Designs with Access Procedures                                 | 70       |

| 4.2.4 A Filter Model                                                                    | 71       |

| 4.2.4.1 Controllability and Observability in the Filter Model                           | 72       |

| 4.2.5 Access Procedures as an Inverse Filter Function                                   | 73       |

| 4.2.6 Definition of an Access Procedure                                                 | 73       |

| 4.3 Using the Test Language to Describe General Behavior                                | 74       |

| 4.3.1 The Actions of a Part Upon a Port                                                 | 74       |

| 4.3.1.1 The Actions of a Tester                                                         | 74       |

| 4.3.2 The Duality of Actions Upon a Port                                                | 75       |

| 4.3.3 The Behavior of Groups of Ports                                                   | 76       |

| 4.3.4 Repetition                                                                        | 77       |

| 4.3.5 Relationships Between Styles of System Descriptions                               | 77       |

| 4.3.6 Examples of Behavioral Descriptions                                               | 79       |

| 4.3.6.1 A Four Bit Adder                                                                | 79       |

| 4.3.6.2 A D-type Flip Flop                                                              | 80       |

| 4.4 Deriving Access Procedures from Behavioral Descriptions                             | 80       |

| 4.4.1 Accessibility Through Flip Flops                                                  | 81       |

| 4.4.2 Accessibility Through A Scan Path 4.4.3 A Method for Generating Access Procedures | 83<br>85 |

| 4.4.4 Matching Access Procedures with Tests                                             | 85       |

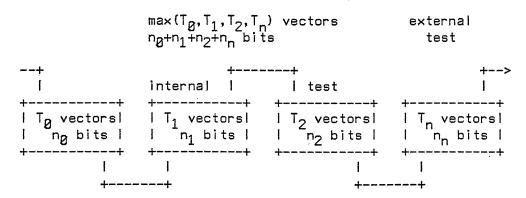

| 4.4.4 Matching Access Procedures with Tests  4.5 Controlled Expansion of Test Vectors   | 86       |

| 4.5.1 Number of Test Vectors in a Test                                                  | 86       |

| 4.5.2 Asymptotic Dependence of Test Size on Number of Cells                             | 87       |

| 4.5.3 Improvements on Asymptotic Behavior                                               | 88       |

| 4.5.3.1 Reducing the Length of Access Procedures                                        | 88       |

| 4.5.3.2 Changing the Branching Factor                                                   | 89       |

| 4,5,3.3 Size of Primitive Cells                                                         | 90       |

| 4.5.4 Actual Dependence of Test Size Upon Chip Size           | 91  |

|---------------------------------------------------------------|-----|

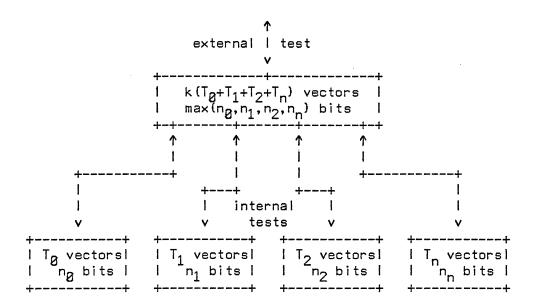

| 4.6 A Perspective on Structured Compositions                  | 92  |

| 4.6.1 Design by Composition                                   | 93  |

| 4.6.2 Composition by Concatenation                            | 93  |

| 4.6.3 Design by Recursion                                     | 95  |

| 4.6.4 A Numerical Comparison of Testing Strategies            | 96  |

| 4.6.5 Other Hierarchical Compositions                         | 98  |

| 4.6.6 Serial and Parallel Testing                             | 100 |

| 4.7 Conclusions                                               | 101 |

| 5. The FIFI Test System: A Reality Test                       | 102 |

| 5.1 Test System Commands                                      | 102 |

| 5.1.1 Loading Test Programs: Define Command                   | 103 |

| 5.1.2 Executing Test Programs: Execute and Immediate Commands | 103 |

| 5.1.3 Miscellaneous Commands                                  | 104 |

| 5.2 Some Examples of the Test Language                        | 105 |

| 5.2.1 Testing the Adder in a Z80 Microprocessor               | 105 |

| 5.2.2 Testing Instruction Decoding in a Z80 Microprocessor    | 109 |

| 5.2.3 Reading the ROM of an 8041                              | 111 |

| 6. The Design of Test Instruments                             | 114 |

| 6.1 Constrained Tests and Tester Design                       | 114 |

| 6.2 High Performance Test Instruments                         | 115 |

| 6.2.1 Conventional Tester Design                              | 115 |

| 6.2.2 Areas for Improvement                                   | 116 |

| 6.2.3 Efficient Use of Test Vector Storage                    | 117 |

| 6.2.4 Interface of the Tester Model to the Test Language      | 118 |

| 6.2.5 Further Refinements in Tester Design                    | 119 |

| 6.2.6 Analogy of Tester Design to the Design of Computers     | 120 |

| 6.2.6.1 Virtual Memory vs the Test Vector Buffer              | 120 |

| 6.3 Requirements for Test Instruments                         | 121 |

| 7. Conclusions                                                | 123 |

| A. Syntax of the Test Language                                | 125 |

| A.1 User Commands                                             | 126 |

| A.2 Procedure Declarations                                    | 126 |

| A.3 Port Declarations                                         | 127 |

| A.4 Typed Value Expressions                                   | 127 |

| A.5 Expressions                                               | 128 |

| Index                                                         | 134 |

|                                                               |     |

## 1. Introduction

This thesis describes the results of an investigation into systematic methods for testing integrated circuits. The central result is a language for describing tests. In the formal presentation of the language, in chapter 2, the ability of the language to represent tests of integrated circuits in the same abstract manner that their designs are visualized is emphasized. The remainder of this document is an exploration and verification of the language's ability to solve a number of the problems of testing integrated circuits. In chapter 1 the usefulness of the language as an interactive tool for the design and debugging of integrated circuits is illustrated. In chapter 3 the ability of the language to describe test of real systems is demonstrated through examples applied to integrated circuits designed with different design styles. In chapter 4 the methods used to generate the examples of chapter 3 are discussed and their general applicability is explored. Chapter 5 describes an implementation of the language. Finally, in chapter 6 a tester design is proposed that can execute the test language more efficiently than conventional testers. The result of this analysis is general technique for designing integrated circuits and their tests that yields reliable results with a predictable amount of effort.

The abstractive properties of the language are aimed at formalizing the manner of testing integrated circuits that is in use today. It has been observed that informally generated tests follow a physical structure (either real or imagined) of the device under test. The specifications of these tests do not generally appear to have any structure, however. It is conjectured that the reason the test specifications do not reflect the structure of the design is that existing test languages do not have the necessary abstractive capabilities. The test language proposed in this thesis attempts to provide this capability.

2

1.1 A Tour Through the Design of an Integrated Circuit

To gain a perspective into the nature of testing complex integrated circuit systems and as

an informal introduction to the test language, this section will follow the design and testing

of a small portion of a complex integrated circuit. As a demonstration of the test system, let

us follow the development of an interesting part, an adder, in an integrated circuit.

A common technique in the design of a complex system is to design and test many of the

component parts separately and then simply compose them into a much larger system. This

technique can be applied to integrated circuit design: a part, such as a memory cell, error

correction unit, or adder, can initially be designed alone, then tested or simulated with a

prototype integrated circuit, and finally incorporated into its environment in the system.

1.1.1 Initial Design and Testing

In the earliest stages our adder is on a prototype chip with all of the inputs and outputs,

and possibly some test points, connected to pads. The design of this chip must be verified.

1.1.1.1 Description of the Pins

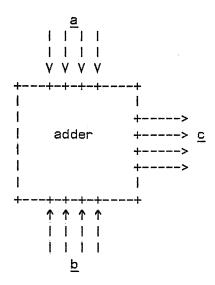

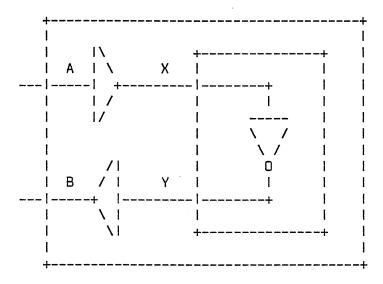

Testing can start off immediately with the prototype chip. Figure 1-1 illustrates such a

chip. The designer would place the chip into the tester and run the test system. Before

testing can begin some preliminary description of the chip must be made: the pins must be

described. This operation might appear as follows:

FIFI>define port a 1 2 3 4;

definitions of pins

FIFI>define port b 5 6 7 8;

FIFI>define port c 9 10 11 12;

An interactive implementation of the test language described here has been constructed

and called FIFI. The FIFI> at the beginning of each line is representative of the prompting

that the test system supplies. The underlined boldface text is the test language input.

Figure 1-1: Illustration of a Prototype Chip

Examples of the test language preceded with FIFI> can generally be typed directly to the test language interpreter. Descriptive information placed to the right in an italic typeface is not part of the test language. These commands specify that there are three logical signals that go in or out of the chip: a, b, and c. Each of these three signals consists of four wires or conductors, and the numbering of these conductors is as shown above.

## 1.1.1.2 Initial Checkout

At this point the function of the prototype chip can be tested. The designer can imagine some inputs that will produce understandable outputs. If the chip were an adder, for example, it might be useful to verify that 2+2 works before an exhaustive functional and timing test is performed. If 2+2 does not generate 4, then a more comprehensive test will be worthless. Similarly, if a chip intended to perform error correction failed to recognize error-free data, then backtracking and carefully inspecting the design would be advisable.

The designer continues his initial testing with:

| FIFI>i a<2,b<2; | line 1 |

|-----------------|--------|

| FIFI>i c!;      | line 2 |

| c:15            | line 3 |

| FIFI>i a<0,b<2; | line 4 |

| FIFI>i c!;      | line 5 |

| c:15            | line 6 |

Lines 1, 2, 4, and 5 start with the letter i. The i is an abbreviation of the word immediate that indicates that the remainder of the line is to be executed immediately. The first line contains two commands of the form p<e. These commands cause the tester to drive a voltage into the pins previously defined. The word on the left, p, is the name of a previously declared port, and the number (in general, an expression e) on the right is a value that will be driven to the pins. The operator < is like an arrow pointing from the expression to the port, indicating the direction of signal flow. The second line invokes immediate execution of the single command c!. Again, the word on the left, c, represents a port declared above, but the operator! causes the tester to print the voltage on those pins instead of driving the pin. The third line is a report of the value of that port.

Although these commands appear to be executed immediately, it is the semicolon at the end of each line that invokes the test steps. Where no; appears at the end of a line the test step would be deferred until one was encountered, similarly multiple; son the same line will cause multiple test steps. The commands are executed in between the time when the return key on the terminal is pressed and the next prompt is printed.

Notice on the third line that the tester is reporting the value of the c port as 15 (decimal), meaning that all four pins have a high voltage.

Having observed the result of 2+2, the values 2+0 are tried. The tester responds again with the result 15, or all pins high.

#### 1.1.1.3 Common Errors

The 2+2 test did not generate the proper response. The designer then tries 2+0, and again gets an improper response. At this point the following thoughts pass through the designer's mind:

- Both responses were 15, and 15 corresponds to all wires high. An unconnected wire will read as high, and therefore perhaps the chip is not in the socket.

- 2. If the power supplies were not connected, not bonded, or corrupted inside the chip then all the outputs would float, causing the observed response.

- 3. Perhaps the assumption that a and b are inputs and c is the output is incorrect, and actually a or b is the output and c is an input. The tester would then be monitoring an input port and would read high.

After considering these possibilities, the designer checks the chip, the power supplies and the layout to determine if any of the above is responsible. He discovers that, in fact, the ground lead is disconnected. The 2+2 test is repeated:

FIFI>i a<2,b<2; FIFI>i c!; a:1 FIFI>i a<2,b<0; FIFI>i c!; a:0

Considerable success: one of the outputs has been observed in both the high and low state in response to changes in inputs. This gives reason to believe that the power supply is intact and that the output drivers function. Otherwise, however, the outputs are all wrong (this is an adder and the result of 2+2 should be 4).

Now the designer draws a picture to see what is happening:

| binary |      |            | binary  |

|--------|------|------------|---------|

| 2 +    | 0010 | 2 +        | 9 9 1 9 |

| 2 =    | 0010 | <b>8</b> = | 0000    |

| 1??    | 0001 | 2??        | 0010    |

6

This picture looks like addition with the binary order of bits reversed. Therefore, the designer checks the layout to verify this possibility, discovers the mistake, and then changes the port definitions with the following commands:

conductors reversed

FIFI>define port a 4 3 2 1;

FIFI>define port b 8 7 6 5;

FIFI>define port c 12 11 10 9;

FIFI>i a<2,b<2;

FIFI>i c!;

a:4

FIFI>i c!;

a:4

FIFI>i c!;

a:2,b<0;

FIFI>i c!;

a:2

The test system is used like a pocket calculator: short expressions can be entered and the results can be observed immediately. In the above example, the designer tried 2+2 and

#### 1.1.2 Exhaustive Checkout

2+0 and received the correct response.

It is now possible to check the adder in considerable detail more-or-less automatically.

Assume that a functional simulation of the device produced a table of inputs and expected responses in the following form: 1

$$\frac{a \leqslant 3,}{a \leqslant 4,} \xrightarrow[b \leqslant 5, \\ a \leqslant 5, \\ \dots etc...} \xrightarrow[b \leqslant 6, \\ \frac{c > 7;}{c > 9;} \\ \frac{c > 11;}{c > 11;}$$

Here, the symbol > indicates that the output of the chip, or port, on the left of the operator is to be sensed and compared with the value on the right. The value on the right is not altered; if there is a difference a global check fail flag is set.

<sup>&</sup>lt;sup>1</sup>This is not as contrived as it may seem: it will later be shown that this notation is an efficient notation to describe simulations.

7

The input output relationship shown here can be applied to the chip by editing the table shown above to the following form and then executing the following tester commands:

contents of file demo

define procedure demo

a<3,b<4,c>7;

a<4,b<5,c>9;

a<5,b<6,c>11;

...etc...

declaration body of procedure

FiFI>read demo

FiFI>execute demo

[check failed]

FIFI>

end

file is read

demo is executed

printed only if bad

The list of inputs and expected responses has been altered in a mechanical way to make a procedure definition. The procedure definition is read to the test system and the procedure name (demo) is made available as an executable test routine. In the example shown, at least one of the comparisons (indicated with a >) failed, causing the statement [check failed] to be printed.

Another technique for functional checkout is to let the tester algorithmically generate a test. Consider, for example, testing an adder exhaustively.

FIFI> immediate (loop i 0 15 FIFI> (loop j 0 15 FIFI> a<i,b<j,c>(i+j)&15;)) FIFI> i takes values 0 1 2... 13 14 15 & is logical and no [check fail] printed

Here the two loop statements cause the controlled variables to take values 0-15, and the third statement performs the test. The third statement uses the loop indices to generate all possible inputs, and uses the ability of the tester to evaluate simple expressions to generate the expected response of the adder. Since the message [check failed] was not printed, the operation of the adder is correct.

#### 1.1.3 Testing an Adder as an Arithmetic Array

The exhaustive test shown above is an efficient test for an adder only if the adder is very small. A larger adder, say 16 bits, would require over four billion test steps. The key to developing a more efficient test for an adder is to test each of its parts separately. Complex devices are generally composed of a number of simpler devices that can be tested independently. The independent testing of all the simpler devices and the verification that they are connected properly is a proper test for their composition. Adders are usually constructed as an array of single bit full adders, and this structure will be exploited to aid in testing.

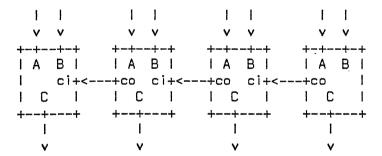

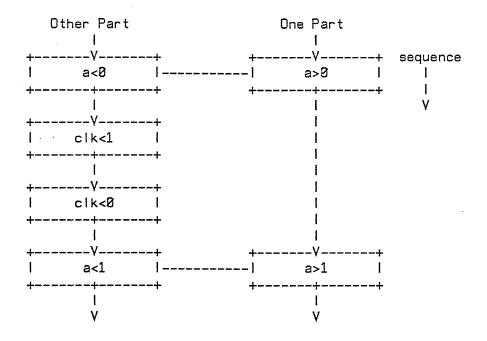

Figure 1-2 illustrates a four bit adder constructed as an array of full adder stages. Each adder stage has three inputs, labeled A, B, and ci (carry input), and two outputs, labeled C (sum), and co (carry out).

Figure 1-2: Four Bit Adder as an Arithmetic Array

Each stage could be tested as follows if the stage were directly available to the tester:

| FIFI>(loop i 0 1 |                                                                     | all combinations of i |  |

|------------------|---------------------------------------------------------------------|-----------------------|--|

| FIFI>            | (loop j 0 1                                                         | j                     |  |

| FIFI>            | (loop k 0 1                                                         | and k                 |  |

| FIFI>            | A <i,b<j,cl<k,< td=""><td>[n] is bit extraction</td></i,b<j,cl<k,<> | [n] is bit extraction |  |

| FIFI>            | $\overline{C}(i+j+k)[0],$                                           | [0] is Isb            |  |

| FIFI>            | co>(i+j+k)[1];))                                                    | [1] is carry          |  |

It is not possible to access the ports ci and co directly, however. These ports can only be

accessed through the stages before and after the stage under test. For example, the ci input to stage N can be set to state x by applying x to both A and B of stage N-1. Using this strategy the following tester code will test all the adder stages except the first and last:

```

FIFI> (loop x 1 2 stages 1 to n-1)

FIFI> (loop i 0 1)

FIFI> (loop j 0 1)

FIFI> A \le (i \le x) + (k \le x - 1),

FIFI> B \le (j \le x) + (k \le x - 1),

FIFI> C \ge (i + j + k) \le (x;)))

```

The first stage cannot be tested this way due to its not having a carry input. Similarly the last stage cannot be tested because of lack of carry output. The following code would be required to test these:

```

FIFI>(loop i 0 1

test first stage

FIFI>

(loop j 0 1

FIFI>

A<i,B<j,C>i+j;))

FIFI>(loop i 0 1

test last stage

FIFI>

(loop j 0 1

FIFI>

(loop k 0 1

FIFI>

\overline{A(i(3)+(k(2),

B<(j<<3)+(k<<2),

FIFI>

FIFI>

C>(i+j+k)[0]<<3;))

```

# 1.1.4 Testing When Embedded in a System

Once our adder has been verified functionally and tested as a separate part, it will be incorporated in its system environment. When put into a new environment testing must again be performed to verify that its composition into the new system is correct, not to mention production testing when the final system design has been verified.

When the adder is not available on a prototype chip, with all it inputs and outputs conveniently available, but embedded in a complex system, verification becomes considerably more difficult.

The strategy to test our adder is to develop a set of software tools to effectively remove the system surrounding the part and then to apply the same tests as before. In other words, we create a software tool that can transform a test of a part into an equally valid test of that part when it is embedded in a system.

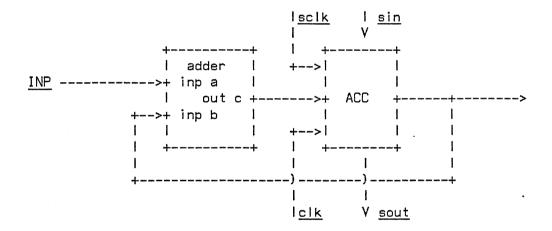

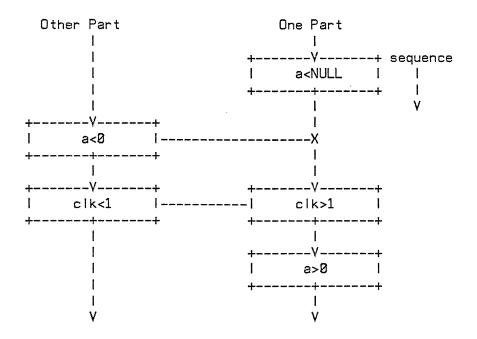

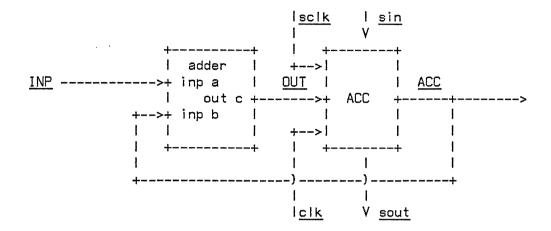

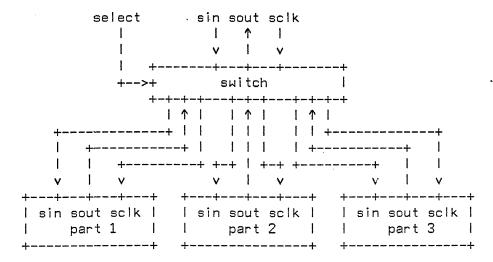

Let us imagine that our adder is embedded in a system with a structure of a conventional one-address accumulator computer; that is, one input of the adder is from an accumulator, and the output always goes to the accumulator. Furthermore, assume that the accumulator contains a scan path that can be used for testing purposes. This structure is illustrated below:

## 1.1.4.1 Describing an Access Procedure

Considering the particular structure of the device shown, the procedure to apply a set of stimuli to the b and c inputs and to observe the a output is as follows: load the c input into the ACC through the scan path, apply the b input to the adder and load the ACC with the result, then unload the a result from the accumulator through the scan path.

A procedure can be constructed to apply two input values and compare one output value to the adder:

| FIFI>procedure access                                                |                                                                                                                                                                                  |  |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| var a b c;                                                           | line 2                                                                                                                                                                           |  |

| (loop i 0 3 sin <c[i],sclk<1;< td=""><td>line 3</td></c[i],sclk<1;<> | line 3                                                                                                                                                                           |  |

| sclk(0;)                                                             | line 4                                                                                                                                                                           |  |

| INP <b,clk<1;< td=""><td>line 5</td></b,clk<1;<>                     | line 5                                                                                                                                                                           |  |

| cik<0;                                                               | line 6                                                                                                                                                                           |  |

| (loop i 0 3 sout>a[i],sclk<1;                                        | line 7                                                                                                                                                                           |  |

| sclk<0;)                                                             | line 8                                                                                                                                                                           |  |

| end                                                                  | line 9                                                                                                                                                                           |  |

|                                                                      | var a b c;<br>(loop i 0 3 sin <c[i],sclk<1;<br>sclk&lt;0;)<br/>INP<b,clk<1;<br>clk&lt;0;<br/>(loop i 0 3 sout&gt;a[i],sclk&lt;1;<br/>sclk&lt;0;)</b,clk<1;<br></c[i],sclk<1;<br> |  |

Lines 1 and 2 declare a procedure with three arguments, a, b, and c. Lines 3 and 4 cause one bit at a time (indicated by the bit subscript [i]) of the c argument to be shifted into the accumulator via the scan path. Lines 5 and 6 cycle the system, causing the adder to be exercised and the result to be put into the accumulator. Lines 7 and 8 unload the accumulator serially and compare the value with the expected result.

#### 1.1.4.2 Testing a Part Through an Access Procedure

Having described how to access the adder, the testing can proceed exactly as if the part were constructed separately. The syntax and semantics of the test language have been chosen to allow the same test description to generate tests either of a directly accessible part, or an embedded part.

The exact syntax required to test the adder when embedded in the system is shown below:

| FIFI>(call access |               | line 7 |

|-------------------|---------------|--------|

| FIFI>             | a<3,b<4,c>7;  | line 2 |

| FIFI>             | a<4,b<5,c>9;  | line 3 |

| FIFI>             | a<5,b<6,c>11; | line 4 |

| FIFI>             | etc)          | line 5 |

Notice that the only change to the code is the inclusion of the text "(call access" at the beginning and a ")" at the end. The first line says that the test language code within the parentheses will refer to testing through the procedure named access. Within these

parenthesis each semicolon causes the procedure to be called. The arguments to the procedure are passed by assignments to the names of the parameters. For example, the first call of the procedure access is with a, b, and c having the values of drive to 3, drive to 4, and compare with  $7^2$ .

The access procedure can be applied to the other tests of the adder developed previously. For example, the test of the adder as an arithmetic array would appear as follows:

```

FIFI>(call access

stages 1 to n-1

FIFI>

(lcop x 1 2

(loop i 0 1

FIFI>

FIFI>

(loop j 0 1

FIFI>

(loop k 0 1

\overline{A(i(<)x)}+(k(<)x-1),

FIFI>

FIFI>

B(j(x)+(k(x-1),

FIFI>

C>(i+j+k)<<x;)))))

```

In a sense the procedure access unlayers the design so the adder appears to be directly available to the user of the test language, when in fact it is not. The concept in the test language of a port is an abstraction of two concepts: the concept of electrical voltages on the pins and the concept of information residing on internal electrical nodes of a device. The concept of the port has the advantages of both the concepts from which it is derived. The application of a port through a tester is straightforward due to its origins as a operation performed on the pins of a device. The generation of tests is greatly simplified by specifying the test in terms of actions on internal nodes. The purpose of the procedure is to implement this abstraction in each particular instance.

$<sup>2</sup>_{\text{The values could also be described as } <3, <4, and >7.$

# 1.2 Strategy for the Design of Tests and Design for Testability

The test language enforces a distinction between the primitive tests and the methods that are used to access these parts. Considerable design flexibility is possible because access procedures for subparts are essentially independent of the construction of the subpart. For example:

- Access procedures for subparts can be specified before the subpart is designed.

- The design of a subpart can be changed without having to change the test specifications for the rest of the design.

- The interface between a part and a subpart may be straightforward enough to allow a division of labor between designers.

## 1.2.1 Primitive Tests

The criteria for generating primitive tests is more dependent upon the technology and physical layout than on the logic of an integrated circuit. Some primitive tests may be devised to assure that all wires adjacent on the silicon are not shorted, or that no wires are open, or that no gates have a stuck-at fault.

The knowledge required to evaluate the types of faults likely to occur includes a knowledge of the technology and the exact placement of transistors and wires. The ideal mechanism for performing this task is a computer program, written with input from physical layout and having representation of the causes of faults. This program would analyze the geometry of portions of the design and generate tests for each portion.

#### 1.2.2 Application of Primitive Tests

The procedures that are used to access the internal parts are dependent solely upon the logical organization of the circuit. The access procedures are a form of a functional description, but an incomplete one in that they describe only one manner of testing each

internal part of the system. It is only necessary, however, to describe one such manner of testing each part, when there may be many.

Since the specification of the access procedures is only dependent upon the functional character of the device, the designer is in the ideal position to perform this task. In an ideal situation, the designer would provide the access procedures at the same time as the register transfer model, or block diagram, of a design is defined.

## 1.2.3 Synergism of Testing and Design

If testing is approached as described above, the test generation task can aid the design task and vice-versa. The access procedures required for testing are functional descriptions relating stimuli applied to the device to internal conditions (i.e. an internal device is tested) that can be verified by simulation. Simulation of the access procedures will serve to verify the functional description. On the other hand, the designer's understanding of the behavior of the device enables him to efficiently specify the access procedures.

#### 1.2.4 Testability

A testability strategy consists of three parts: (1) the possible augmentation of the hardware of system to include mechanisms that simplify the application of primitive tests, (2) methods for applying primitive tests through the augmented hardware, and (3) the actual generation of the primitive tests.

Previous researchers have formalized some testability strategies. In [Bouricius 71] a testing strategy called D-calculus is described for generating primitive tests for combinational logic. The D-calculus computes all tests from the pins of the chip, and potential simplifications due to the logical structure are not exploited. When the computation of tests directly from the external pins becomes too difficult, selected internal nodes can be

connected to the pins to improve diagnosability [Hayes 74]. In LSSD, [Eichelberger 77], the access of internal state is aided by transforming state registers into a serial shift register. The manner of accessing internal state in LSSD is firmly defined and a designer has no freedom to make changes that would optimize performance.

The test language allows testability strategies to be formalized. Tests for combinational logic generated by the D-calculus would be formalized by the test language as tests with no access procedures. LSSD can be formalized by a very simple access procedure that clocks the serial shift register. Testability strategies for specific applications would include descriptions of access of internal state through relatively complex (i.e. more complex than a single shift register) hardware. The test language is therefore a testability strategy generator.

# 1.3 The Design of Testers

#### 1.3.1 Test Generation Modes

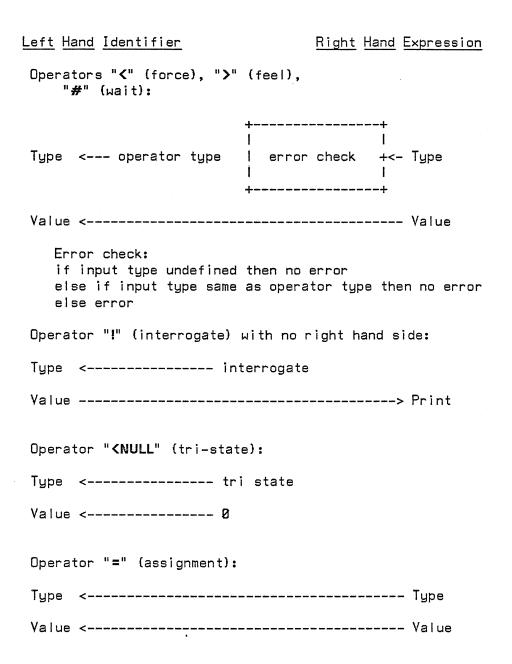

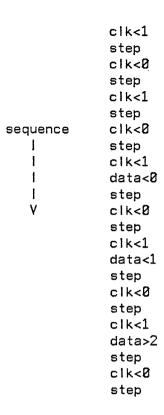

One test generation mode is the sequential mode. In sequential mode, the test is generated by the continuous execution of the test language. The output of the test language system is a series of commands to alter values on pins and perform test steps. Sequential mode has the advantage that the entire test is never instantiated in storage at one time, and therefore large test matrix storage is not necessary.

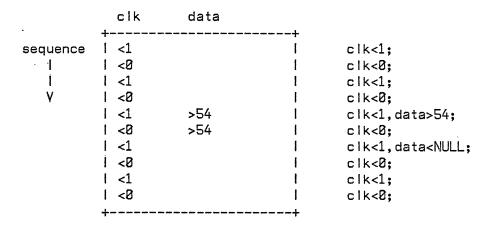

An example of sequential test output is shown below. Each line is a tester command.

Tester commands accumulate until a step command is encountered, and then are all applied simultaneously.

FIFI>i (loop i 1 2 data(i,clk(1;clk(0;)

Sequential output is used in the tester that is presently interfaced to the test language system.

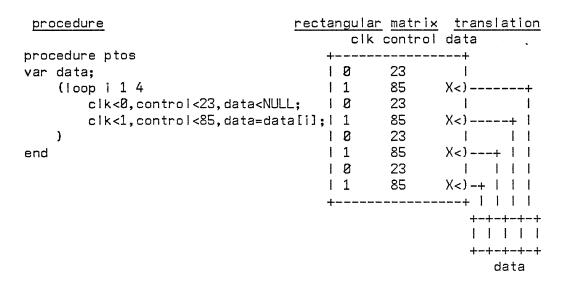

A second test generation mode is the rectangular matrix, or timing diagram, mode. In this mode the test system generates a single large static test matrix. A test matrix consists of a series of test vectors, each test vector being one row of the matrix. Each test vector represents the stimulus and response of the different ports of the device during one test step, and the vertical dimension represents the sequence of the test. The rectangular matrix mode of output matches more closely the operation of conventional testers where the entire test is resident in memory for the entire duration of the test.

The rectangular matrix test mode is illustrated below:

FIFI>i (loop i 1 2 data<i,clk<1;clk<0;)

|               | data | clk |

|---------------|------|-----|

| +             | +    | +   |

| 1<1           | 1<1  | 1   |

| <b> &lt;1</b> | 1<0  | 1   |

| 1<2           | l<1  | 1   |

| 1<2           | 1<8  | 1   |

| +             |      |     |

FIFI>

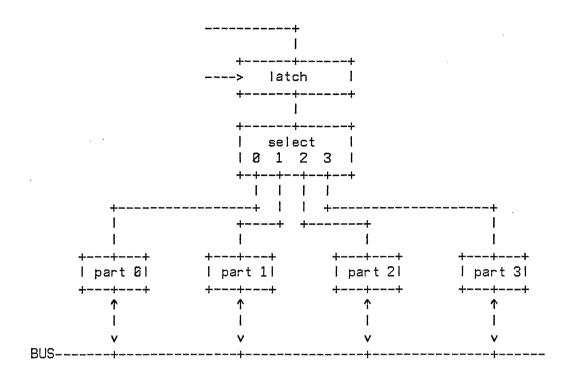

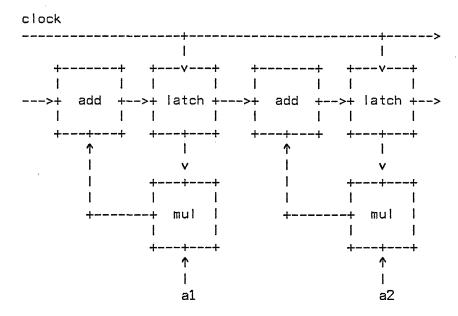

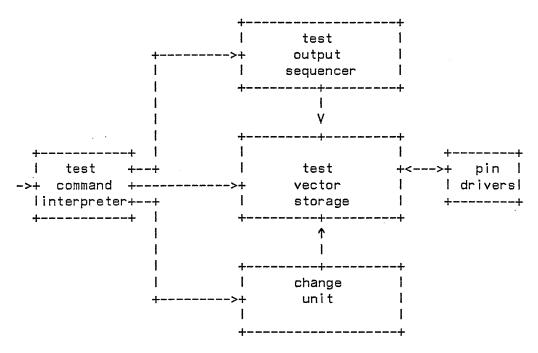

#### 1.3.2 Tester Construction for the Test Language

Testers can be made more efficient if they execute this test language. The test language lends itself well both to dynamic generation of tests and to the simple application of test vectors stored in a memory. Since the size of tests, measured in numbers of steps, grows astronomically as the complexity of devices increases, a system that needs to store all test vectors simultaneously has a considerable advantage. The speed at which tests can be generated sequentially may be much less than is required for efficient testing.

A tester can be constructed to accept sequential commands and store test vectors. Testing procedures that are short and do not invoke any other testing procedures, called low level testing procedures, would be executed by storing the rectangular matrix representation in memory and dumping the memory to the test head when necessary. The low level procedures contain very few test vectors, but are executed many times. Sequential test generation can be used for the high level procedures that invoke the low level testing procedures. Since a complete low level testing procedure is executed between steps of the high level procedures, the rate of high level execution can be much less.

A tester/test language system of this type would consist of a sequential test generation unit to generate tests in a very flexible, but slow manner, and a buffer test generator to buffer the high speed, but simple, tests and invoke them on command of the sequential test generation unit.

#### 1.3.3 Interface of the Test Language to Simulators

The function of the test language in describing electrical signals to be applied to a chip is very similar to the function of the input description language of a simulator. In this section, let us consider the possible application of the test language as an input language to a

simulator.

Conventionally, simulators have two types of input, a description of the device as an assemblage of parts, and the description of the stimuli to be applied to the device. Typically, the response of the simulated device can only be printed for visual verification by the user. Simulators of this type include circuit level simulators such as MSINC [Young 76], and SPICE [Nagel 73], and switch simulators such as MOSSIM [Bryant 81] [Bryant 82], and system level simulators such as the functional simulator in [DeBenedictis 79].

In interfacing the test language to a simulator, most of the functions applicable to testers retain the same meaning: performing test steps corresponds to running the simulator, the < and > operations would effectively drive and sense the value at an internal port, etc.

Some possibly subtle differences exist, however. A simulator has access to internal as well as external ports. It is possible to do a <, >, or ! operation on a port that is completely internal to the chip. Force operations can have considerably greater flexibility with a simulator. The simulator may be able to force a port *gently*, only changing the voltage on a capacitive port, or may force a port *firmly* by supplying DC current [Bryant 82].

The test language has the capability of sensing the output of the simulation through > operations and making decisions concerning the correctness of the simulation. If observing the output of the simulation manually was desired, the ! operation could be used.

Since simulation and testing play similar roles in the design process, a common language to both could be tremendously advantageous. Simulation is performed when a design is partially completed and limited verification of its operation is desired. Since simulations are of limited accuracy due to approximations about the characteristics of transistors and the layout, true verification through testing is necessary. In both the simulation and testing of an integrated

19

circuit the information provided and the results obtained are the same: a stimulus is specified and the results are observed or verified. A common language would give the effort expended in developing simulations double duty; it could be used for testing also.

## 1.4 The Value of an Interactive, Non-Embedded Test Language

Previous work in the testing field has usually been in the direction of embedded test languages. Earlier work used a language such as Fortran and embedded commands to manipulate tester hardware. More recently high level test systems are being developed wherein test commands are embedded in Pascal. Current work includes interpreters written in the embedding language which implement a more machine independent test language.

For reasons discussed later in this section, this work is opposed to the strategy of developing embedded test languages.

#### 1.4.1 ATLAS

The test language ATLAS [IEEE 80] is defined by IEEE as a machine independent language for testing. Unfortunately, ATLAS is not specific to integrated circuit testing: it is equally efficient for describing tests for jet engines as adders. ATLAS's generality may make integrated circuit descriptions less compact than desired.

ATLAS is basically a fortran style programming language with a large number of additional statements related to testing. An example of an ATLAS statement is shown below:<sup>3</sup>

M00840 VERIFY, (VOLTAGE), DC SIGNAL, UL +0.5V LL -0.5V, CNX HI SK1-A LO SK1-B \$ performs a > operation

ATLAS has the advantage of not being tied to the particular hardware of test instrument.

<sup>&</sup>lt;sup>3</sup> [IEEE 80], page 105.

20

1.4.2 FACTOR

Another embedded test language is Fairchild's FACTOR programming language [Fairchild

80], the control language for the series 20 testers. The series 20 testers contain a general

purpose computer designed specifically for the tester with interfaces to various electrical

interfaces and a 1024 vector test memory. The test language is basically Fortran with

statements for manipulating the pins directly and for loading the 1024 vector test memory.

Once loaded, the test memory can be dumped to the pin electronics to perform a functional

test.

The Fairchild tester contains a precision measurement unit, or PMU. The PMU can be

connected to a number of different pins and drive or sense voltages of currents with high

accuracy. The following are example statements to drive a current of -1 uA into pin number

26:4

CPMU PIN 26;

FORCE CURRENT -1E-6, RNG1;

connect to PMU exponential notation

1.4.3 ANGEL

ANGEL [Snoulten 81] is an example of a test language midway between embedded and

stand-alone. ANGEL is a block structured imperative language with embedded testing

commands constructed for testing. ANGEL differs from other embedded test languages

because the embedding language is original. Like other embedded languages, ANGEL includes

flow control and conditional statements.

An example of ANGEL code is shown below:

<sup>4</sup> [Fairchild &O], pages 9-18 and 9-19.

```

do t=7,12

increment count

if (count .eq. F 'hex) then .eq. is from fortran

set CO .co is a port

else

clear CO

end if

apply COUNT and CO [t=[7,12]

end do

```

#### 1.4.4 The FIFI Test Language

The FIFI test language is a non-embedded interactive language. By making the language non-embedded a number of advantages are obtained:

- 1. The language can be easily interactive. Most embedding languages require a compiler, and hence cannot be interactive.

- 2. Test specifications can be much more concise if the syntax of a programming language is not required.

- A non-embedded language can constrain tests to have certain regularity and simplicity properties that may allow the test to execute quickly or on simple hardware.

- 4. Portability. An embedded language is unlikely to be adopted as a portable test specification language because (1) the embedding language is probably not portable, and (2) there will likely be competition from other embedding languages.

## 1.5 Summary

The purpose of this work is to demonstrate that testing can be made into a systematic task. The testing task described in later chapters interfaces to design and layout in well defined ways. The generation of tests is partitioned into subtasks corresponding to different physical or logical parts of the system. This means small changes in a system will require only small changes in the test specifications.

# 2. A Notation for Describing Integrated Circuit Testing

The test language introduced informally in the previous chapter will now be described formally. In section 2.1 the meaning of the digital signals that flow between a tester and a device is formalized. In section 2.1.2 an algebra is developed for manipulating these digital signals in an abstract manner. In section 2.2 the assembly of these signal manipulations occurring at different times into test matrices is discussed. Chapter 3 continues with examples of the test language.

# 2.1 Abstract Elements of Digital Electrical Signals

Electrical information on wires is more complicated than just ones or zeros. Information flows in a particular direction, or may not flow at all, and has various electrical and timing properties. A Signal will often be encoded on a number of conductors, or as a sequence of values separated in time. The test language uses an element of information that is a concise and understandable way of manipulating electrical signals.

#### 2.1.1 Elements of the Algebra

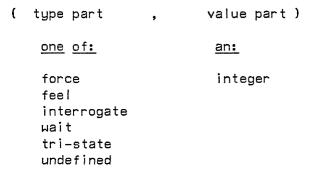

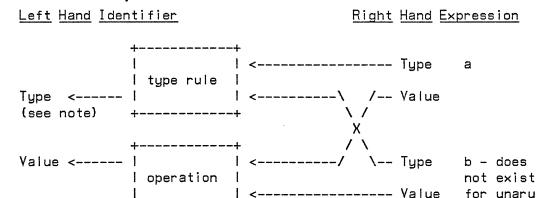

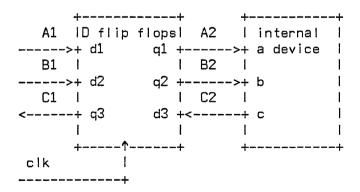

The testing algebra deals with elements called *typed values* that are *ordered pairs* consisting of a *type part* and a *value part*. Figure 2-1 illustrates a typed value.

Figure 2-1: A Schematic Representation of a Typed Value.

The value of a digital signal will be represented as an integer. Each conductor in a multiple-conductor signal will be represented by one bit in the binary representation of the integer. The number of relevant bits is determined by the number of conductors, or the degree of time multiplexing of the signal.

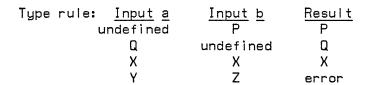

In addition to the value of the signal, the direction of flow is relevant. The obvious concept that there are two directions, in and out, is too restricted. The algebra utilizes six directions, or types: force, feel, interrogate, wait, tri-state, and undefined. The physical meaning of these are described in figure 2-2.

Force: The value part is forced upon the device under test. The tester output

drivers are enabled.

Feel: The outputs of the device under test are compared with the value part.

If there is a difference a global error flag is set.

Interrogate: The outputs of the device under test are sampled and the result is

printed for interactive examination by the operator.

Wait: Advancement of the test step is delayed until the outputs of the

device under test are equal to the value part. This action may be

subject to a timeout.

Tri-state: The tester outputs remove drive and the outputs of the device under

test are ignored.

Undefined: Causes an error. The undefined type is generated by constants and

must be changed to a 'defined' type before application to pins. Application of type undefined to a pin indicates a probable user error.

Figure 2-2: Types of Information in a Tester and Their Meanings

The reader may notice two interpretations of the typed values:

- The tagged data interpretation is that the typed values are like data in a tagged data architecture machine. In a tagged data architecture computer data has a type part, describing the data as, for example an integer, floating point number, or procedure, and a value part, such as the bits of the integer or floating point number, or the address of a procedure. The value of the data is determined only when absolutely necessary, either by using the integer or floating point value, or executing the procedure [Organick 73]. In the test algebra the available types are force, feel, etc. and the execution of a test step depends upon the types of the typed values applied to the pins.

- The algebraic interpretation is that the typed values of the algebra are elements of a mathematical set with operations defined among its elements. The elements of the set are ordered pairs. The first element of the pair is

selected from a set of five types. The second element of the pair is an integer modulo  $2^n$ , where n is predetermined. As will be described later, this mathematical set has a subfield relating to the value, or integer, part. Other aspects of the structure are more complicated.

#### 2.1.2 Ports

A port is a group of conductors available to the test instrument. This group of pins is always referred to as though it were an integer, that is, there is a MSB pin and a LSB pin. In addition, all pins in the group have the same type, i.e. all are either forced, felt, waited upon, etc. Figure 2-3 defines a port called addr that consists of 16 conductors. Conductor 5 is the MSB and conductor 30 is the LSB. The syntax of port definitions is discussed in appendix A.3.

FIFI>define port addr 5 4 3 2 1 40 39 38 37 36 35 34 33 32 31 30;

Figure 2-3: Example of a Port definition.

## 2.1.3 Equations and Assignments

In general, a typed value assignment is like a conventional assignment statement: the right hand side is an expression that is evaluated and the result is associated with the port on the left hand side. In the test language expressions are typed value expressions and evaluate to an ordered pair consisting of a type and a value. The entities that may appear on the left side of an assignment are carefully controlled. The left side may specify either a port or a parameter to a testing procedure. A port is a name associated with one or more electrical conductors of the tester. A typed value assignment to a port is the basic action used to make a test, and will often be called an action.

#### 2.1.3.1 Assignments

The simplest assignment operator is =. The = operator simply takes the typed value generated by the right hand side and associates it with the entity on the left hand side.

Other assignment operators exist that are less general, but more frequently used. These operators coerce the type of the assignment to their particular type, ignoring the type of the right hand side. Figure 2-6 defines the different assignment operators and figure 2-4 shows examples of the different operators and explains their meaning. The exact syntax of assignment operators is shown in appendix A.4.

| name       | <u>operator</u>                                    | <u>type of result</u> | <u>value</u> of result |

|------------|----------------------------------------------------|-----------------------|------------------------|

| force      | x <y< td=""><td>force</td><td>value-of-y</td></y<> | force                 | value-of-y             |

| feel       | x>y                                                | feel                  | value-of-y             |

| interrogat | e ×!                                               | interrogate           | •                      |

| tri-state  | × <null< td=""><td>tri-state</td><td></td></null<> | tri-state             |                        |

| wait       | ×#y                                                | wait                  | value-of-y             |

| equal      | x=y                                                | type-of-y             | value-of-y             |

Figure 2-4: Examples of Assignment Operators of Different Types

Except for interrogate, which will be discussed later, this interpretation of the type of an assignment statement is consistent with the original interpretation of the types in typed values. In all the types discussed associating the typed value with an electrical conductor of the tester requires additional data. This information will be driven through the output drivers of the tester if the type is force, or compared with the voltages sensed from the chip is the type is feel.

#### 2.1.3.2 Expressions

The syntax of expressions in the testing algebra is similar to conventional expression syntax: an expression consists of constants or variables interspersed with unary or binary operators. Parentheses can be used. Figure 2-5 shows examples of typed value expressions. See appendix A for a general discussion of the syntax of the test language.

and appendix A.5 for the specifics of expression syntax.

|    | <u>expression</u> | <u>value in (type,value) notation</u> |  |

|----|-------------------|---------------------------------------|--|

| а  | 4                 | (undefined, 4) see note               |  |

| b  | X                 | (type-of-X,value-of-X)                |  |

| C. | . X+4             | (type-of-X,value-of-X + 4)            |  |

(Note that constants have type undefined.)

Figure 2-5: Examples of Typed Value Expressions

The full meaning of the semantics of the operators is very different from the conventional interpretation of operators. The differences, however, always involve elements of type interrogate. We will discuss the conventional interpretation, where the use of interrogate is excluded. The changes required for type interrogate are discussed later.

Note: this interpretation does not apply if type is interrogate.

Figure 2-7: Conventional Interpretation of Arithmetic Operators

operator

In the conventional interpretation the evaluation of the type and value parts is independent. The value of an expression is the result of the indicated operation on the

Figure 2-6: Different Assignment Operators

value parts of the two operands. A best guess is made for the type of the result. If one of the inputs is undefined (perhaps because it is a constant) the result will be the type of the other operand. If both inputs are of the same defined type than the result will be of that type. If the inputs are of different defined types then no good guess can be made.

#### 2.1.4 Specification of Analog Tests

The concept of the typed value has more generality than is exploited here. In addition to the specification of a digital signal value and direction, the typed value could have information describing the voltage levels corresponding to a one and a zero, or timing information describing the relative timing of the signal transition with respect to the start of the test step. A more complete set of potential attributes of a typed value are listed below:

Type One of force, feel, interrogate, wait, or undefined.

Value Binary information.

Voltages One and zero voltage levels for drive and sense. If these four numbers

are not specified then the last specified values are used. If no

voltages were ever specified, the system defaults are used.

Timing Skew Two timing values, one for the transition time for forced values and one

for felt values. If left unspecified, the last specified values are used,

or a system default.

Glitch Detection A flag that may assume the values of true and false. If glitch detection

is enabled, hazards encountered during feel operations will cause the

feel operation to fail.

Output Load Several real numbers that specify the type of output load to be applied

to a pin. One such number might be a parallel capacitance, and another

might be current load.

The list of possible features that can be included in the typed values is not practically bounded. Special purpose testing tasks might require testers with special hardware which could be invoked through additional attributes of the typed value. For this reason, future test systems should allow special user defined attributes in the typed values, and should implement only those supported in hardware.

## 2.2 Organization of Digital Manipulations into Test Matrices

All tests of digital systems ultimately consist of a series of *test steps*. Each test step is essentially a typed value assignment to a group of conductors on the device under test. The changes in the state of the tester outputs for each test step are described by a *test vector*. A test consists of many test vectors applied in sequence, and these are termed a *test*

matrix.

Section 2.1.2 describes an algebra for manipulating information relevant to test instruments. That algebra is suitable for describing the information to be applied to a single output of the test instrument. This section describes how to combine many of these to form a test matrix.

## 2.2.1 A Restricted Test Language and Testing Efficiency

The test language is capable of generating *non-adaptive tests* only. A non-adaptive test is a test where the application of the test does not depend upon any information obtained from the device under test. Non-adaptive tests are sufficient for testing a large class of devices, including nearly all currently manufactured chips<sup>5</sup>.

An arbitrary non-adaptive test can always be represented as a finite fixed set of test operations (typed value assignments) associated with the pins of the device under test. Since the set is finite it can be evaluated, stored, and manipulated. The test can also be stored in the high speed memory of a tester and played against the device under test at a constant high speed.

The description of an arbitrary adaptive test will require a general purpose language, i.e. a language capable of computing all computable functions. A test program written in a general purpose language may produce an infinitely large test. Infinitely large tests cannot, of course, be stored and manipulated. The evaluation of an arbitrary computable function may require an arbitrary number of machine steps, and hence the test cannot necessarily be

<sup>&</sup>lt;sup>5</sup>A sufficient condition for a chip to be testable with a non-adaptive test is that the chip have a reset sequence [Seitz 71]. An example of a chip that is not testable with a non-adaptive test is a chip containing a counter that can neither be reset nor loaded.

generated at a fixed rate.

The restrictions in the test language over general purpose programming languages are as follows:

- There are no conditionals. Conditionals could be of two types: (1) dependent upon information returned from the device under test, and (2) dependent only upon program variables. Conditionals of type 1 would result in an adaptive test, and conditionals of type 2 can be eliminated by macro expanding the test.

- 2. There are no variables to represent tests. Tests can only be created, they cannot be stored. The test language could, as an optimization, recognize repeated tests and store them, but it is not possible for the test language to require that this be done. This gives the test language the ability to handle arbitrarily large tests with a finite memory.

- 3. Information flow is toward the device under test only. Information cannot be returned from the device under test except in very special, restricted, ways. Information return is limited as follows: (1) there is a go/no-go flag, and (2) interrogate operations cause information to be returned to the operator. This allows reasonable physical design of testers.

The test language is really a weak programming language: there is no floating point, no I/O, no conditionals. It is impossible to compute prime numbers using the test language. In fact, it is impossible to do anything with the test language except generate tests.

It is important that the language be viewed as a notation for describing tests, rather than as a programming language adapted to testing. These restrictions of the language will force the test designer to specify tests in a particular programming style. This style is enforced by the limitations on the choice of constructs available. The single allowable programming style emerges as the most structured and efficient to execute.

<sup>&</sup>lt;sup>6</sup>The typed value operations previously described have a considerable power that, in other languages, would require conditionals. In a sense, the test language does not eliminate conditionals, it merely confines them to primitive operations on the defined data types.

#### 2.2.2 Elements

Description of a matrix always begins with a description of its *elements*. In the test language the elements are typed value assignments, or actions.

Figure 2-8 illustrates some examples of typed value assignments. Notice in figure 2-8, line 4 that the word 'addr' appears twice. The occurrence on the left refers to port, and the occurrence on the right is a variable.

FIFI>define port clk 6;

FIFI>def port addr 5 4 3 2 1 40 39 38 37 36 35 34 33 32 31 30;

FIFI>clk<1;

port clk driven high

FIFI>addr<addr[0:6]; FIFI>addr<addr[7:13];

FIFI>

FIFI>

FIFI>clk<1,clk<0;

line 4

port addr driven to

low and high parts

of variable addr

undefined, error condition

Figure 2-8: Illustration of Pin and Variable Assignments

The last line in figure 2-8 illustrates the condition where the same port is assigned different values in the same test step. This action corresponds to an incorrectly formed test and is a user error.

### 2.2.3 Test Matrices

There are two interpretations that can be applied to tests generated by the test language, the *static interpretation* and the *dynamic interpretation*. Each of these interpretations is the best view in some circumstances: the static view allows the most abstract visualization of large tests, and the dynamic view has greater flexibility in describing complex manipulations within a test.

The static interpretation is based upon the test matrix. A test matrix is an array of typed

values specifying a typed value for each pin of the device under test for every step. Figure 2-9 illustrates a small test matrix<sup>7</sup>.

logical pins--->

|                                                            | <u>clk</u>                                                                | db <u>5</u>                                                                                                                                                                                         | <u>db4</u>                                                                                                                                                            | <u>db3</u>                                                                                                                              | <u>db2</u>                                                                                                | <u>db1</u>                                | >1<br>_db0                |

|------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------|

| test 1<br>steps 2<br>1 3<br>1 4<br>V 5<br>6<br>7<br>8<br>9 | +<br>  <1<br>  <0<br>  <1<br>  <0<br>  <1<br>  <0<br>  <1<br>  <0<br>  <1 | <null< td=""><td><null< td=""><td><null< td=""><td><null< td=""><td><null <0="" <null="">1 &gt;1 &gt;1</null></td><td><null i<="" td=""></null></td></null<></td></null<></td></null<></td></null<> | <null< td=""><td><null< td=""><td><null< td=""><td><null <0="" <null="">1 &gt;1 &gt;1</null></td><td><null i<="" td=""></null></td></null<></td></null<></td></null<> | <null< td=""><td><null< td=""><td><null <0="" <null="">1 &gt;1 &gt;1</null></td><td><null i<="" td=""></null></td></null<></td></null<> | <null< td=""><td><null <0="" <null="">1 &gt;1 &gt;1</null></td><td><null i<="" td=""></null></td></null<> | <null <0="" <null="">1 &gt;1 &gt;1</null> | <null i<="" td=""></null> |

|                                                            | +                                                                         |                                                                                                                                                                                                     |                                                                                                                                                                       |                                                                                                                                         |                                                                                                           |                                           | +                         |

Figure 2-9: A Test Matrix

Figure 2-9 is a complete test consisting of 10 steps. The first four steps cycle the clock twice and the data bus is ignored by the tester. Steps 5-8 force the values 0 and 1 to the data bus in two clock cycles. Steps 9 and 10 feel the data bus values for the integer 2 while cycling the clock.

The dynamic interpretation is based on the continuous production of tester commands by the test language system. These tester commands are illustrated in figure 2-10.

Figure 2-10 shows two types of commands: commands specifying operations to be performed on ports, and a command to perform a test step. Test vectors are delimited by the word step in figure 2-10. Typed value assignments between the steps are included in the same test vector.

$<sup>^{7}</sup>$ In future illustrations **<NULL** will not be printed, but the space will be left blank.

Figure 2-10: Continuous Stream of Tester Commands

# 2.2.4 Static Interpretation

A test can be viewed as a *test matrix*. The elements of the matrix are *typed values* to be applied to the physical conductors of the chip. The horizontal axis of the matrix is calibrated in the physical conductors, or ports, and the vertical axis in test steps. Figure 2-11 includes a picture of the test matrix representation.

The following notation is used in representing a test matrix: each entry consists of a typed value pair depicted by the assignment operator corresponding to that type, and a constant representing the value. For sake of appearance, ports that are ignored by the tester, ports that would be represented as <NULL, are left blank.

The syntax of the test language representation of a test matrix is constructed according

# Test Matrix Representation

### Textual Representation

#### conductors ->

Figure 2-11: Simple Test Matrix and Representation.

### to the following rules:

- Each force, feel, etc. on a port is described by a typed value assignment, discussed previously.

- 2. Multiple actions performed on the same step are separated by commas, and form a test vector.

- Each test vector is terminated with a semicolon, and conversely, semicolons separate test vectors. A number of test vectors separated by semicolons are called a test matrix.

A convenient manner of organizing this representation into lines of test is to place each test vector on a separate line, and to end each line with a semicolon. Figure 2-11 shows an example of a test matrix and its representation.

#### Some comments are in order:

- When a test step is performed the action occurs first on the force operations, later on the feel operations, and last on the interrogate operations. The test system follows this convention and actions not written in this order will be put into this order by the test system. *Execution* of an typed value assignment then consists of scheduling an operation to occur at the appropriate *phase* of the test step.

- When a test step occurs and a particular port is not specified as the destination of any typed value assignment, then the port state is retained. This means, for instance, that if the purpose of a test step is merely to change a

clock, only the change of the clock need be specified, and the states of all the other ports that will not change need not be respecified. On the other hand, if the outputs of a port are to be sampled only once then the feel condition must be explicitly withdrawn or the comparison will occur (and possibly fail) later.

The last vector of a test matrix according to this representation must end with a semicolon. Lack of a trailing semicolon means that the test step is not yet complete. This concept is subtly useful but is described only with the dynamic interpretation.

#### Other operators exist:

- The *plus* operator combines test matrices, overlaying them row by row and aligned at the top. The length of the resultant test matrix is the maximum of the lengths of the original matrices.

- The comma operator, previously described as operating on typed value assignments, can operate on matrices also. Two matrices separated by commas result in a matrix that is the concatenation in sequence of the two matrices, the leftmost matrix occurring first. (The semicolon operator operates similarly, except it produces an empty test step at the point of concatenation.)

- In addition, some labor saving constructs exist. There is a *looping* construct that when applied to a test matrix will repeat the matrix a number of times. There is also a step construct that generates a specified number of empty test steps.

Figure 2-12 illustrates these operators.

The static interpretation is useful because it allows test matrices to be instantiated and stored for fast execution. Test matrices may be larger than the memory available in the test system, and hence use of this interpretation is limited to small test matrices. Larger test matrices are executed dynamically.

# 2.2.5 Dynamic Interpretation

The static interpretation makes a distinction between test matrices and typed value assignments, and also a restriction that all test matrices end with a semicolon. The dynamic interpretation, while being more complex, eliminates these irregularities and allows greater flexibility in describing tests.

| (loop I | 1 5 clk<1;clk<0;) |     | (data<3;data<4;) ,<br>(loop I 1 3 data<5;data<6;) |   |  |  |

|---------|-------------------|-----|---------------------------------------------------|---|--|--|

| clk     | data .            | clk | data                                              |   |  |  |

| · <1    |                   |     | <3                                                | + |  |  |

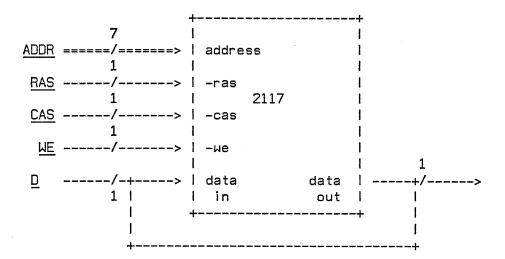

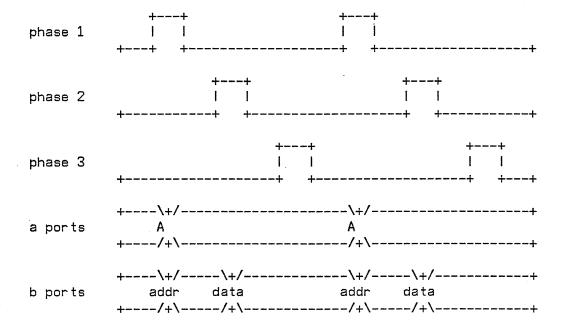

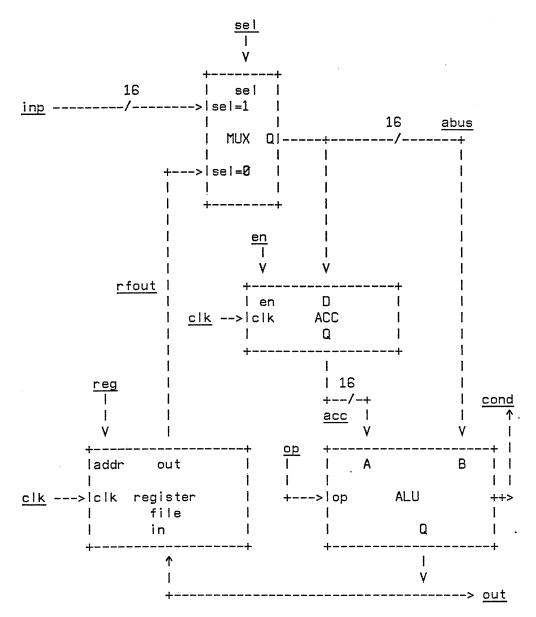

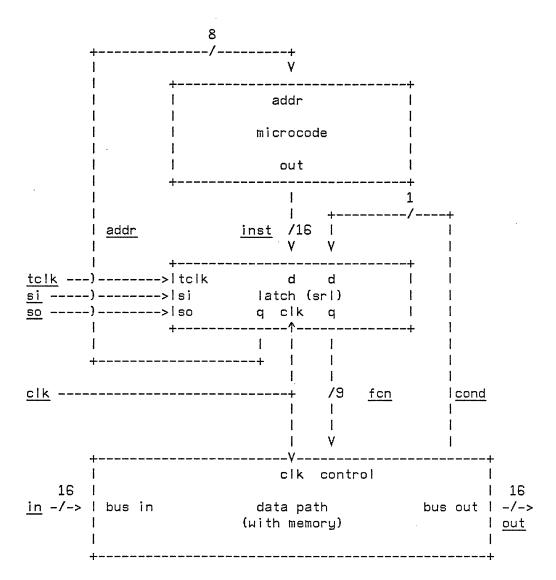

| l <0    | 1                 | 1   | <4                                                | 1 |  |  |