# HOMOGENEOUS MACHINE CURRENT STUFF

The Homogeneous Machine was also called the Nearest Neighbor Concurrent Processor (NNCP) and later the Cosmic Cube

Contributions by: Erik P. DeBenedictis Charles L. Seitz William C. Athas

This notebook was archived December 1982 and digitized January 1, 2008.

HOMOGENEOUS MACHINE

CURRENT STUFF

### HOMOGENEOUS MACHINE TECHNICAL PLAN

9 January 1982

Erik P. DeBenedictis

Charles L. Seitz

Caltech Computer Science

Copyright (C) 1982 Caltech. Copying is allowed.

The research described in this document was sponsored by the Defense

Advanced Research Projects Agency, ARPA Order number 3771, and monitored by the Office of Naval Research under contract number NOO014-79-C-0597.

No. 4705

This in an internal working document of the Caltech Computer Science epartment. Some of the ideas expressed in this document may be only artially developed or erroneous. All of the materials included are the property of Caltech and its sponsors. Distribution of this document outside the immediate working community is discouraged; publication of this document is forbidden.

#### Table of Contents

| 1. | Introduction                          |

|----|---------------------------------------|

|    | 1.1. The Proposed Machine             |

| 2. | Architectural Innovations             |

|    | 2.1. Independence of Processors       |

|    | 2.2. Allocation of Memory             |

| 3. | Potential Performance of the Hardware |

|    | 3.1. A Model of Computation           |

|    | 3.2. Cost/Performance                 |

|    | 3.3. Long Range Projections           |

| 4. | An Overview of the Implementation     |

|    | 4.1. Main Array of Processors         |

|    | 4.2. Dedicated Host                   |

|    | 4.3. Mainframe Hosts                  |

| 5. | Proposed Plan of Action               |

|    | 5.1. Current Status                   |

|    | 5.2. Timetable for Future Work        |

|    | 5.3. Cost Estimates                   |

#### 1. Introduction

This homogeneous machine project is a product of more than five years research in concurrent processing by two departments at Caltech. Research in concurrent computation in the computer science department started with theses by Browning [Browning 80] and Locanthi [Locanthi 80], and continues with a thesis in preparation by Dick Lang, and work by Chuck Seitz [Seitz 81]. All this research is shared an emphasis toward implemention with higher and higher density integrated circuits. The computer science department has been planning to construct a machine of the genere for several years.

Our colleagues in High Energy Physics have been plagued by a lack of suitable computing technology to solve some fundamental physics problems. In the course of our collaboration it became evident that our research had studied architectures of the sort ideal for their physics problems. Our collaboration with High Energy Physics has caused us to select some particular versions of the architectures that we have been studying as the most likely to be useful. Given our theoretical interest in the architectures and the practical use sought by High Energy Physics we have decided to act now to construct a homogeneous machine.

This document describes the plan of the computer science departement.

The plan of High Energy Physics is described in [HEP 81].

#### 1.1. The Proposed Machine

The homogeneous machine proposed here is a hypercube machine consisting of 64 identical microprocessors interconnected in a 1, 2, 3, and 6

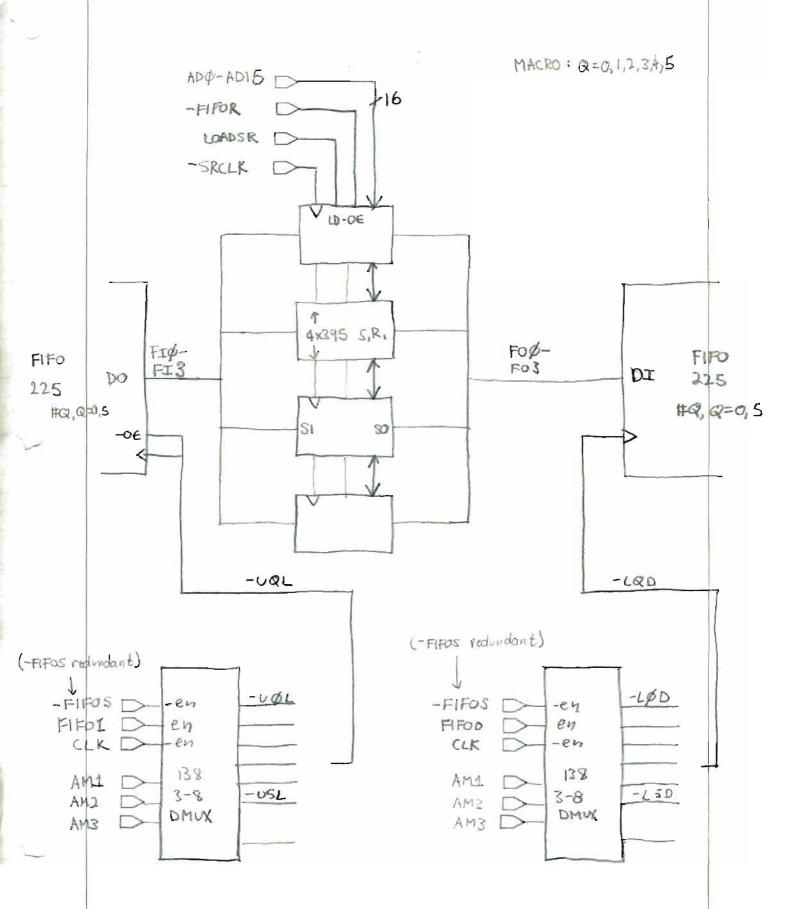

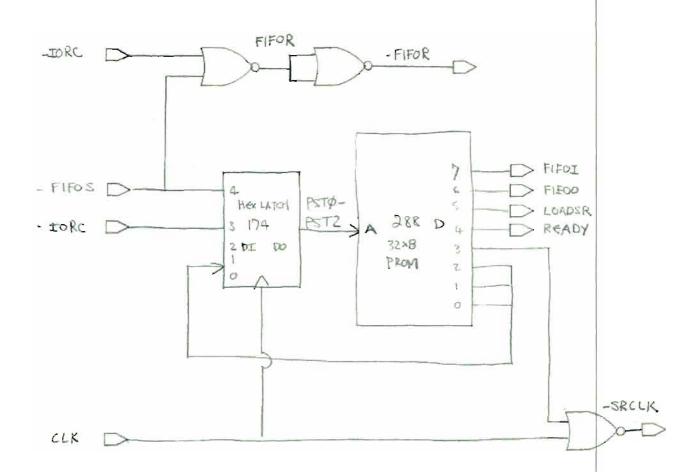

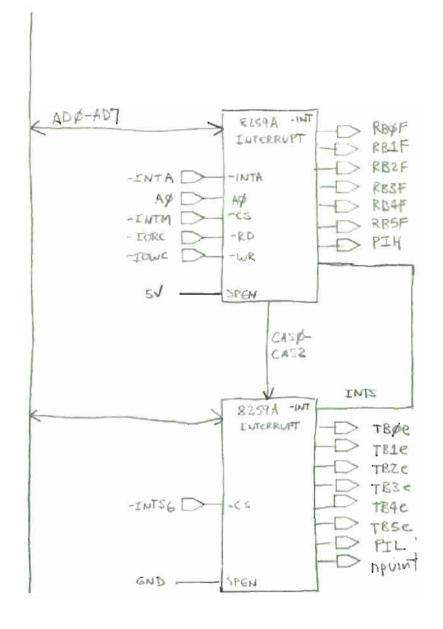

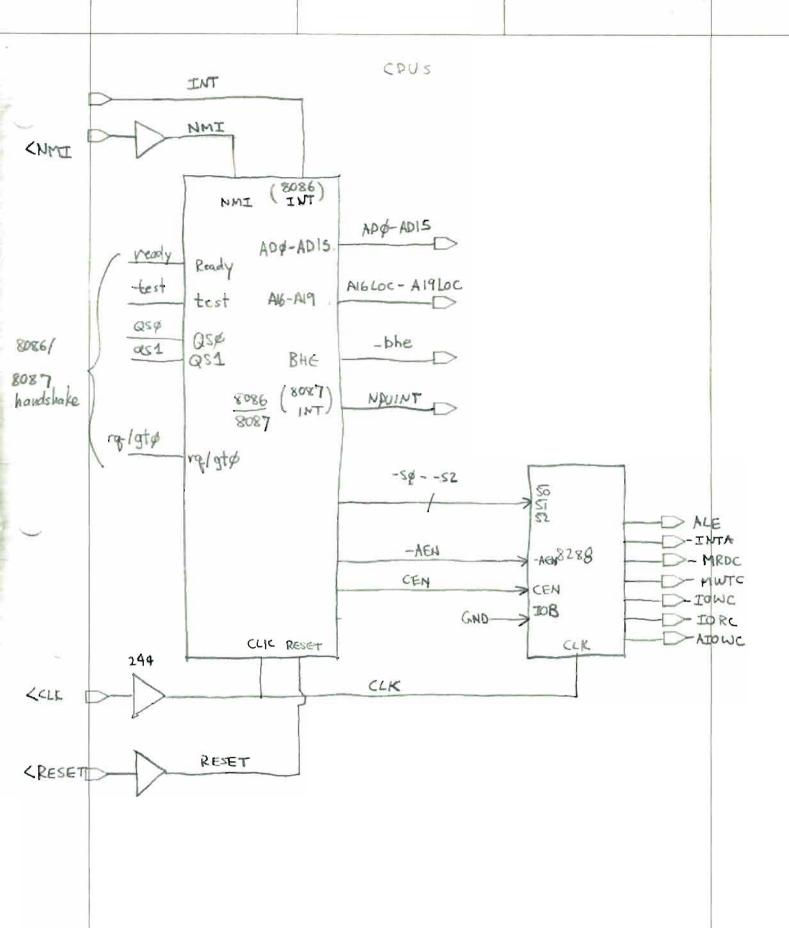

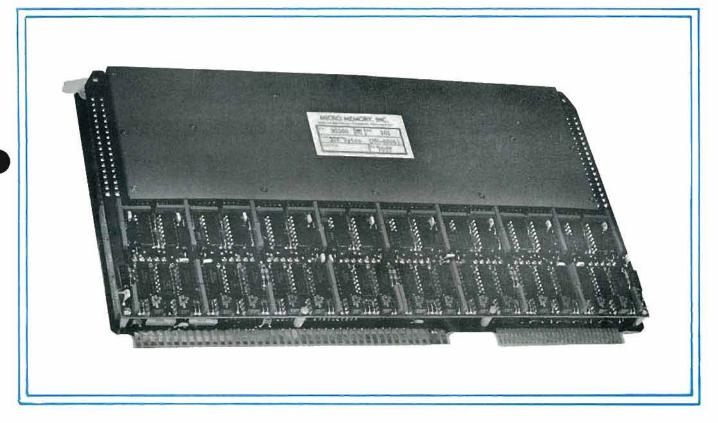

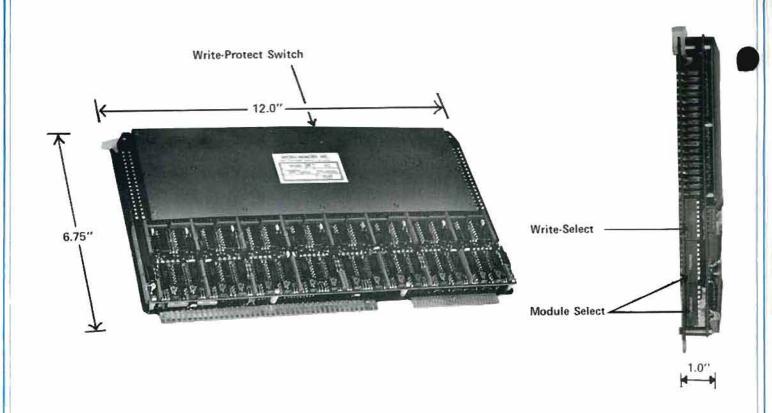

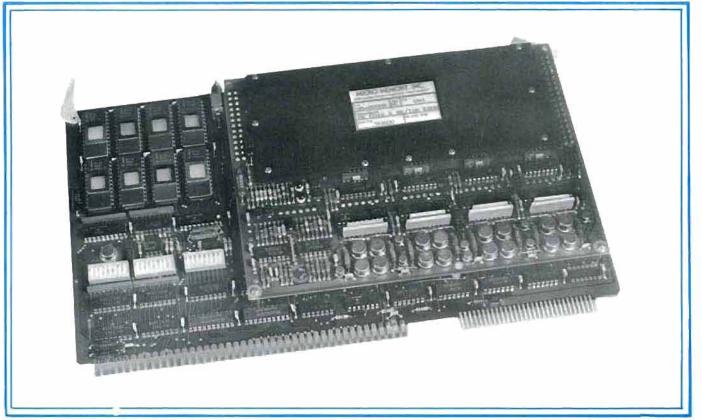

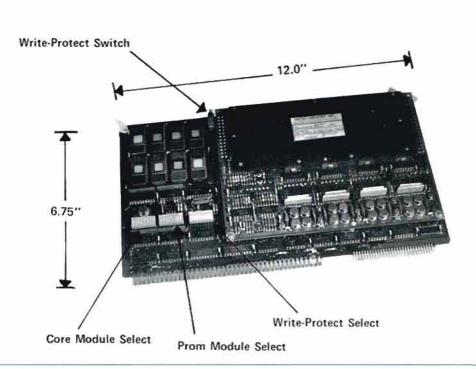

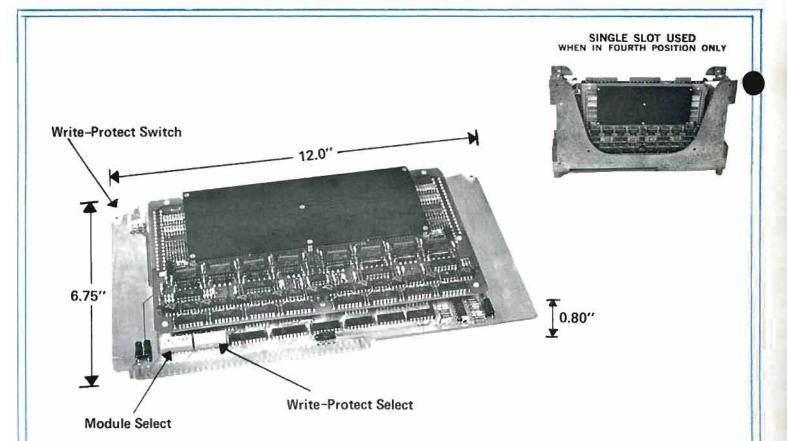

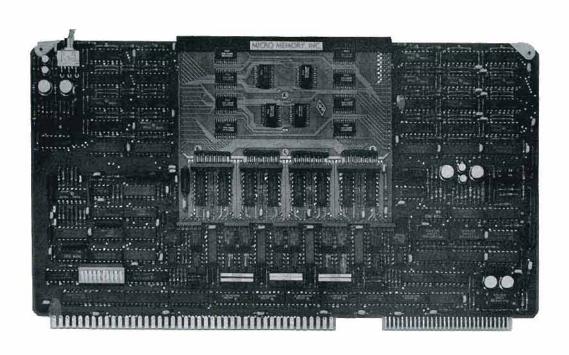

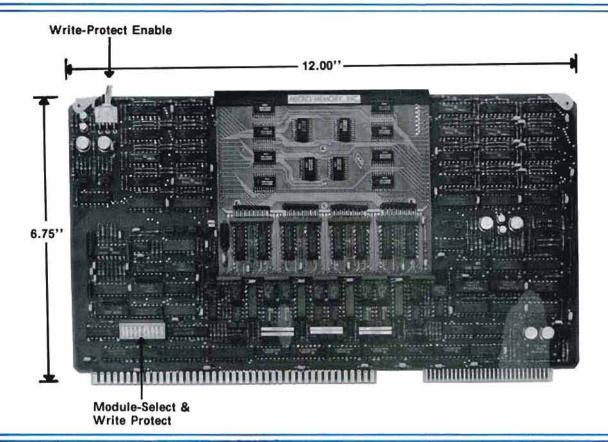

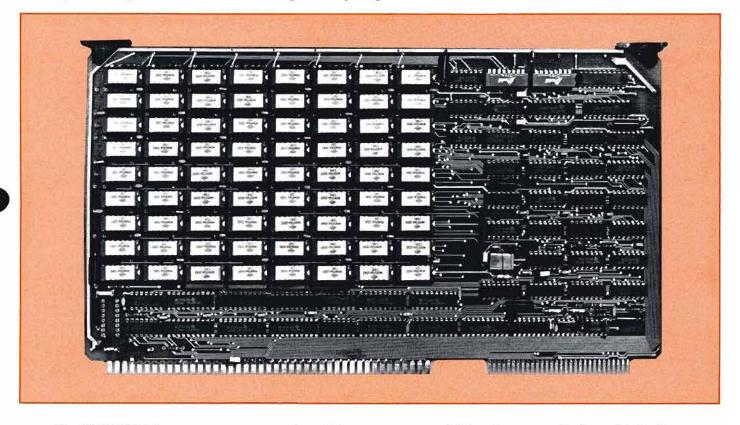

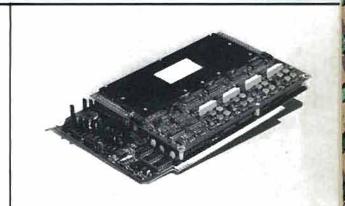

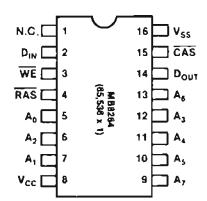

dimensional array. Each of the processors consists of about 77 chips, including a 8086 microprocessor, a 8087 floating point chip, 1/8th of megabyte of RAM, and six bidirectional interfaces to other processors. The processors will be constructed on 64 printed circuit boards mounted in a custom backplane. The hypercube machine will consist of this array of processors and a single dedicated host processor that will control the array.

The class of problems that can be solved by such a machine is limited. There is absolutely no intention of the machine ever being able to execute a conventional program. Certain very limited classes of problems can be solved efficiently, and many of these problems are so large and important that a special purpose architecture is justified.

This paper will discuss the architecture, physical design, and some applications for a machine of this architecture.

#### 2. Architectural Innovations

The architecture of the hypercube machine is new. Previous multiprocessors were constructed to allow direct implementation of many conventional computer programming constructs. These multiprocessors typically included special hardware to allow each processor access to the memory of others. Using the shared memory semaphores could be implemented, but only with extra hardware. The hypercube machine discards many of the

All four dimensionalities can be obtained simultaneously with the proper structure.

conventional programming constructs, and the hardware to implement them.

#### 2.1. Independence of Processors

A popular architectural direction in multiprocessor architecture has been to make a single sequential process execute faster by putting more processors onto the same memory. The results may be communicating sequential processes, as in C.mmp and CM\*, or a high speed execution of a single sequential process, as in the dataflow machines of Dennis.

Tightly coupled multiprocessor architectures have a range of problems: the hardware cost grows faster than linearly with the size of the machine, and the efficiency of the software decreases as machine grows. The hardware will invariably contain a large switching network to route memory accesses or commands between arbitrary processors. A large switching network has a large parts inventory, and will operate slowly due to long wires and complex switching.

Research at Caltech indicates that architectures communicating through message passing have a brighter future than those with tight couplings or shared memory. Consider the effect of decreasing feature size on the design of a hypercube machine processor. Figure 1 shows the progress of the design from the present size of 50-77 chips/system to a one or two chip implementation a decade from now.

| Feature Size | Chip Count |

|--------------|------------|

| 3 microns    | 50-77      |

| l micron     | 5-8        |

| 0.5 micron   | 1 – 2      |

Figure 1: Effect of Decreasing Feature Size on Processor Chip Count

Consider the advantages of a 1-2 chip/processor hypercube machine: 1) the processors would be very fast because of very few off chip delays, 2) chowould be interconnected very regularly and with very high density, and 3) the parts inventory would be small, i.e. one or two.

The hypercube machine connects processors with high bandwidth, but very loose connections. Each of the processors is quite small and standard, allowing maximal use of LSI 'glue' components. The compactness of the the system and short buses allows for high clock rates. In a nearest neighbor configuration all wires are short.

#### 2.2. Allocation of Memory

The trend in multiprocessor research is to move away from the single large computer to more and more smaller and smaller computers. This trend is almost valid because present mainframes are very much larger than an optimal computer. The trend can be followed too vigorously, however produce computers that are too small to be cost effective.

Multiprocessors have been studied where the processors are too small. Two examples are the tree machine studied at Caltech [Browning 80] and the systolic array studied at CMU [Kung 80]. Both machines use processors that, in today's technology, would be less than one chip in size. The tree machine processors are programmable, containing about 1K bytes of RAM. The systolic array processors contain no program RAM, but are effectively programmed in their internal arithmetic layout.

One (but only one) of the proposed network configurations.

In the process of tree machine research at Caltech, Browning and the author programmed a number of useful algorithms for the tree machine and studied their performance. A pattern was noticed in the results: tree machine algorithms tend to require as much time to load the problem into 3 the machine and to unload the answer as is required to solve the problem.

Estimates of the necessary size of a tree machine required to solve a useful problem tend to be large. Tree machines too small to store an entire problem would have to solve a problem in parts, swapping the parts between a secondary storage and the tree machine. The effect of swapping is to degrade performance by orders of magnitude, making that an unreasonable alternative. The only solution is to make the machine large enough to store an entire problem. With only a fraction of their IK byte storage available for data storage an unreasonably large number of processors are required.

The reason for this phenomenon is that the processors have so little memory that they cannot perform meaningful computation for very long. The solution to this problem for the hypercube machine is to reduce the number of processors and give each processor much more memory. The speed of the machine is reduced to a more reasonable level because the processors must multiplex their computations. Since a larger portion of the machine is low

For example, sorting N numbers requires N steps to load the problem and N to unload the answer. Sorting is accomplished during the loading process where log N processors cooperate to load a number into the proper processor while maintaining proper order. The average number of sort operations performed by each processor is log N, whereas the number of steps to load and unload the problem is 2N.

cost memory, the cost of a machine required to perform a useful problem is reduced.

#### 3. Potential Performance of the Hardware

Let us consider the economics of processing with an array of microprocessors operating concurrently. Another paper examines the question of whether full concurrency can ever be achieved, and also whether a large enough body of problems exist to justify constructing such a machine [HEP 81].

#### 3.1. A Model of Computation

In this preliminary analysis we will adapt a very simple view of computation: we will assume that a problem solution requires some amount of memory, and that some number of operations are performed. Those problems that will execute efficiently on the hypercube machine will have the characteristic that they can be partitioned into a multiplicity of processors. In this partitioning, each processor will have a fraction of the total memory of the problem, and will perform the same fraction of the total operations performed in the problem. An array of n processors will be equivalent to a single conventional computer with n times the memory and n times the speed.

#### 3.2. Cost/Performance

Let us consider compare the costs of such a machine and a conventional computer. The dominant cost in the hypercube machine is the cost of a single board that contains the basic processor. Let us examine the commercial viability of a hypercube machine by estimating the market cost

of a hypercube machine and comparing its performance with competitive products.

Since the single board of the hypercube machine would be produced in such large volume, its cost would follow the same economics as semiconductor RAM systems today. We will estimate the cost market of a hypercube machine by analogy to a large RAM system.

At today's market prices semiconductor RAM costs \$15,000 per megabyte. Semiconductor RAM boards usually consist of boards populated approximately 75% with 16K RAM chips. One megabyte of RAM would consist of 512 RAM chips and 170 support chips by the above model. The cost per chip is therefore \$22.

The hypercube machine described in this paper consists of a processor with 77 chips. Each processor has a 0.5 MIP performance on normal instructions, a floating point speed of 20 uS, and 1/8 mB of memory. At \$22 per chip the cost is under \$1700 per processor.

A DEC 11/780 (VAX) has a floating point speed of about 1 uS, and could reasonably support 10 mB of memory. A machine in such a configuration would cost \$400,000. If the same \$400,000 were spent on hypercube machine processors at \$1700 each, 235 could be purchased. A hypercube machine of 235 processors would have an equivalent floating performance of 0.1 uS, and 30 mB of memory.

<sup>4</sup> These prices include power supply and backplane.

A CRAY-1 has a floating point speed of 15 nS, and costs \$15 million with a large amount of memory. To obtain the equivalent floating poperformance with hypercube machine processors at 20 uS per processor, 1,333 would be required. These 1,333 processors would additionally have 166 mB of memory, much more than the CRAY-1, and would cost \$2.2 million.

#### 3.3. Long Range Projections

These prices are conservative. For example, approximately 2/3 of the chips (but less than 1% of the transistors) in the processor are SSI/MSI chips in the interprocessor interface section. Should a large effort be made to build such machines, these chips could be reduced to 1 or 2 LSI chips. Also, the processor used is the oldest 16 bit CPU and the floating point unit is the first constructed by the industry.

As discussed previously, improving technology will continue to decrease the number of chips per processor to a limit of one or two. Since processors are so amenable to IC implementation, their price/performance will increase much more rapidly than average.

In summary, the hypercube machine being constructed at present has a potential price/performance that is about 7 times better than products available today. Even given a substantial inefficiency in software, the hypercube machine will be noticeably better and either a VAX or CRAY-1. Future improvements in microprocessor technology will drastically improve this already good situation. More efficient CPUs and floating point units, and special interprocessor communication chips should reduce price/performance by an order of magnitude.

#### 4. An Overview of the Implementation

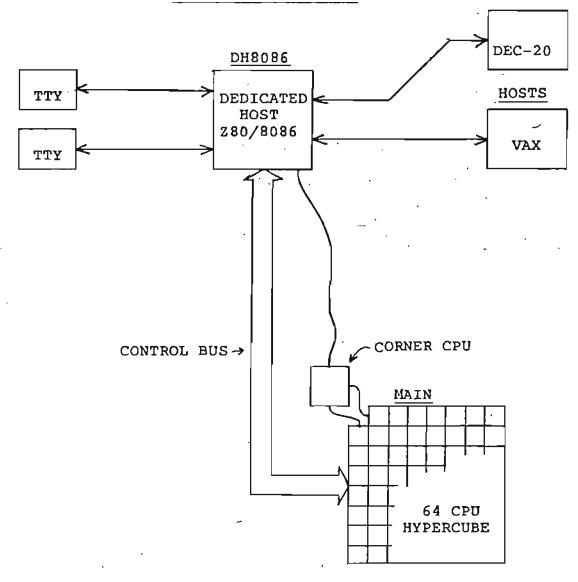

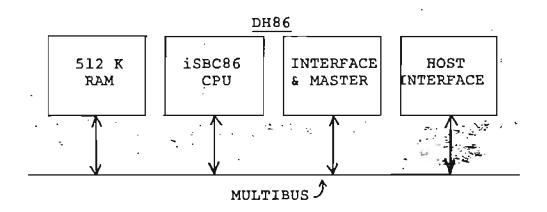

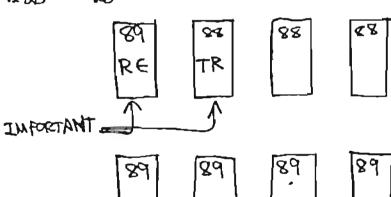

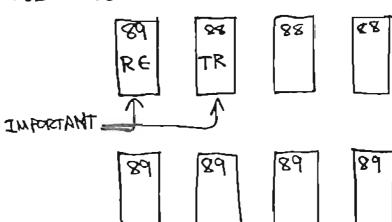

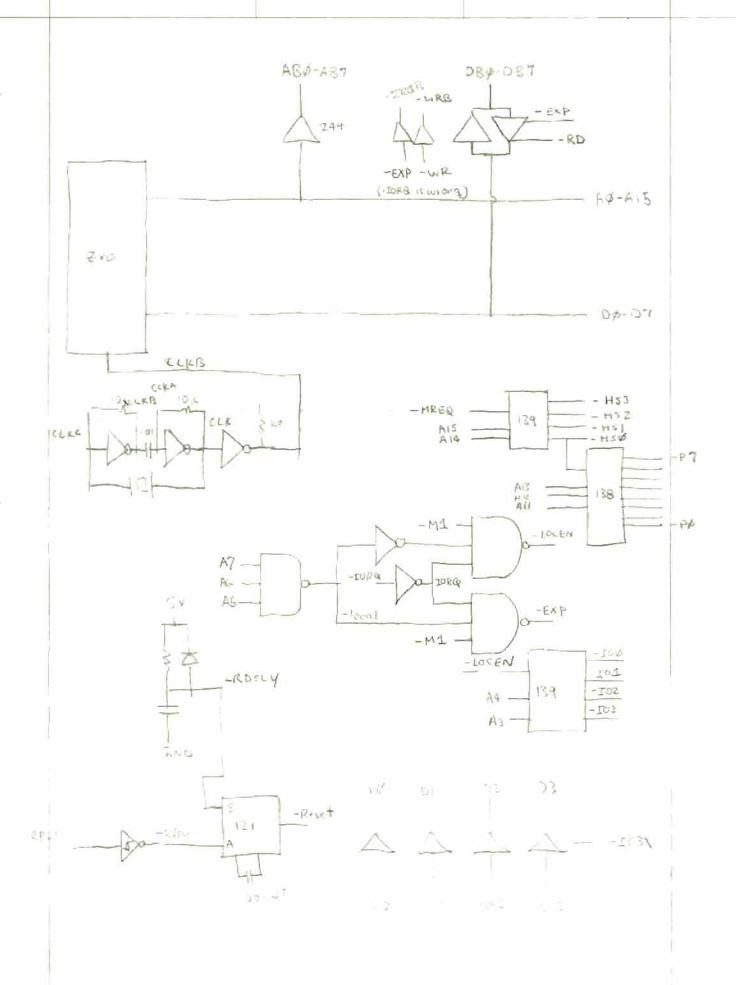

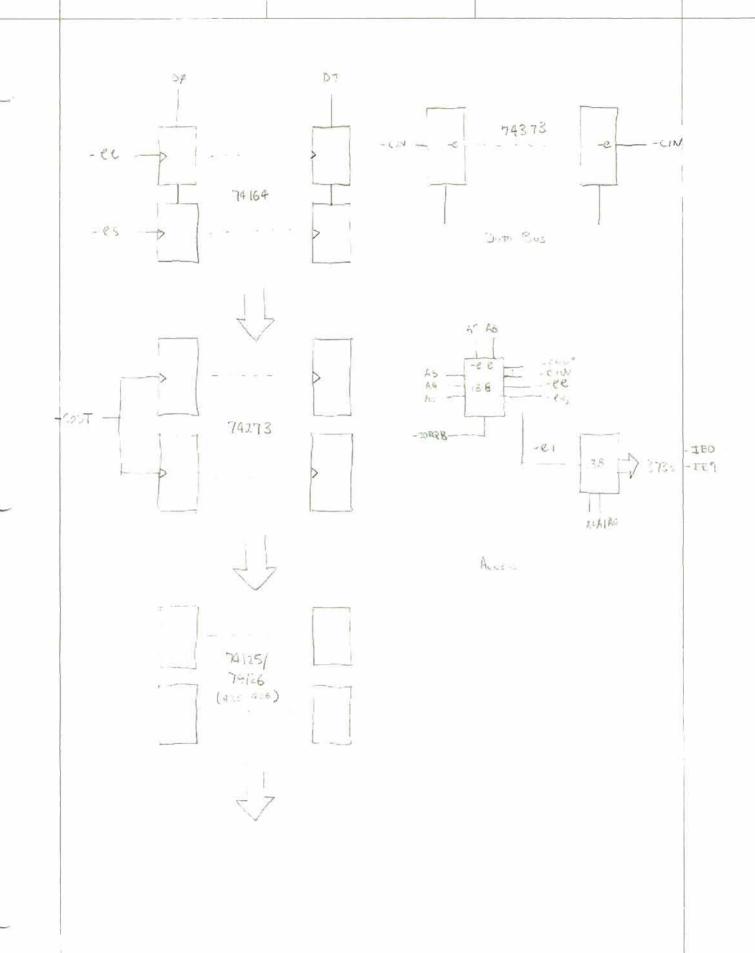

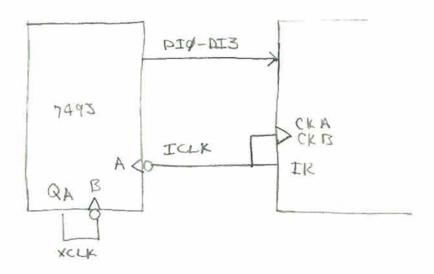

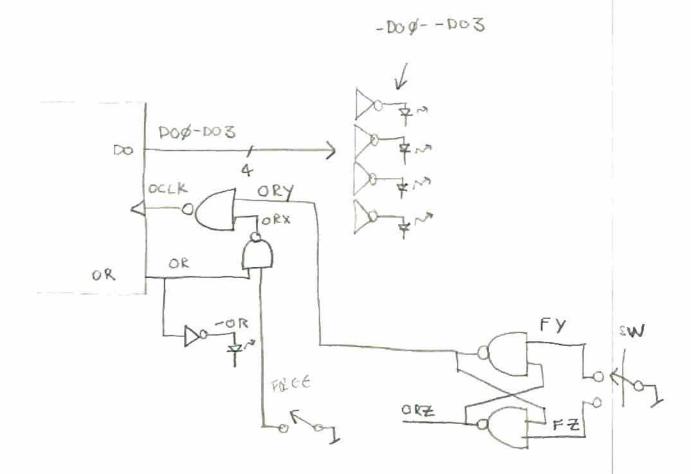

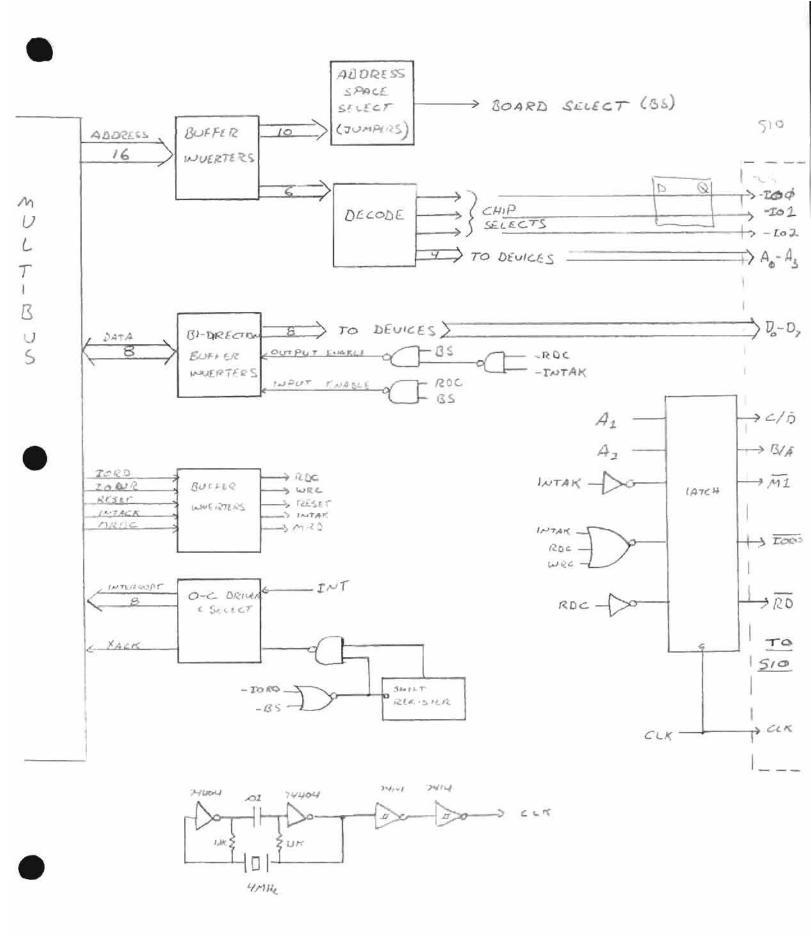

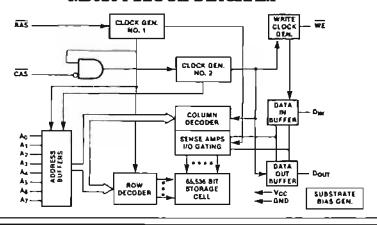

The hypercube machine can be divided into three parts for convenience of explanation: 1) the array of microprocessors, called the main processors, 2) the dedicated host, which controls the array and interfaces to 3) the host (or hosts), which are mainframe machines the perform compiling of code for the machine. Figure 5 is an overview of these parts and their interconnections.

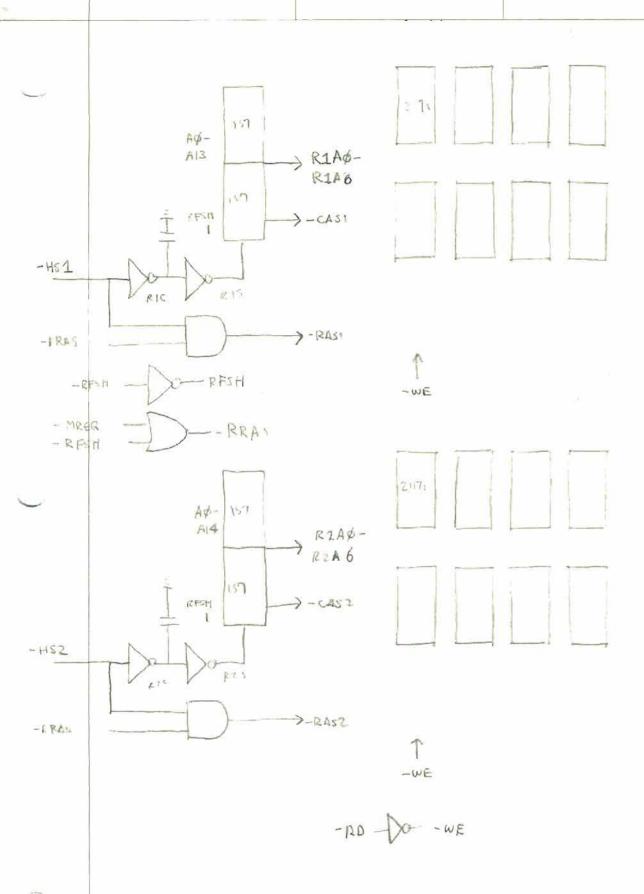

#### 4.1. Main Array of Processors

The main array is essentially a multi-dimensional array of microprocessors. With one exception, these are all identical processors that connect only among themselves in a tightly connected network. One of the processors has one extra connection, however that connects the array to the rest of the world.

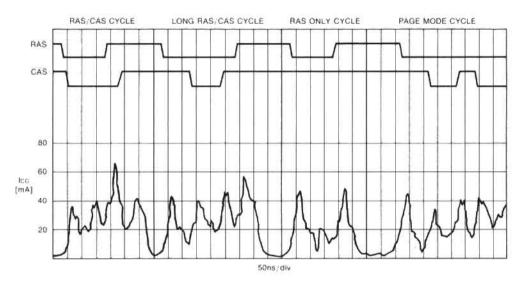

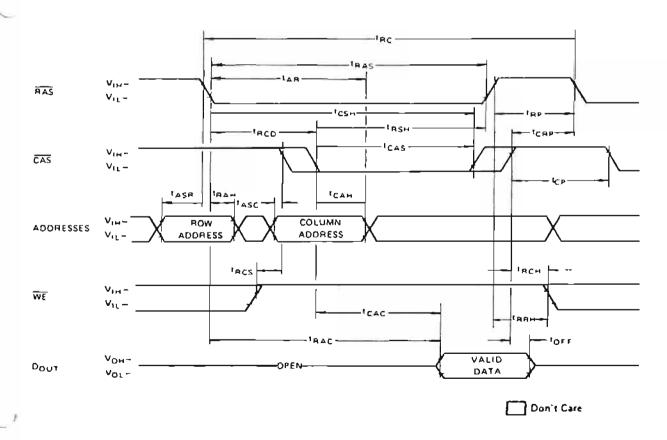

All of the main processors are connected by a control bus. This bus allows sharing of functions that are same for all processors, such as clock and memory refresh. The control bus also provides a flexible but low bandwidth global communications capability for use by diagnostics and as a network-wide software debugging aid.

The processors are interconnected by fully asynchronous bidirectional connections. The hardware supports a 64 bit interprocessor message by generating interrupts only when complete messages can be input or output.

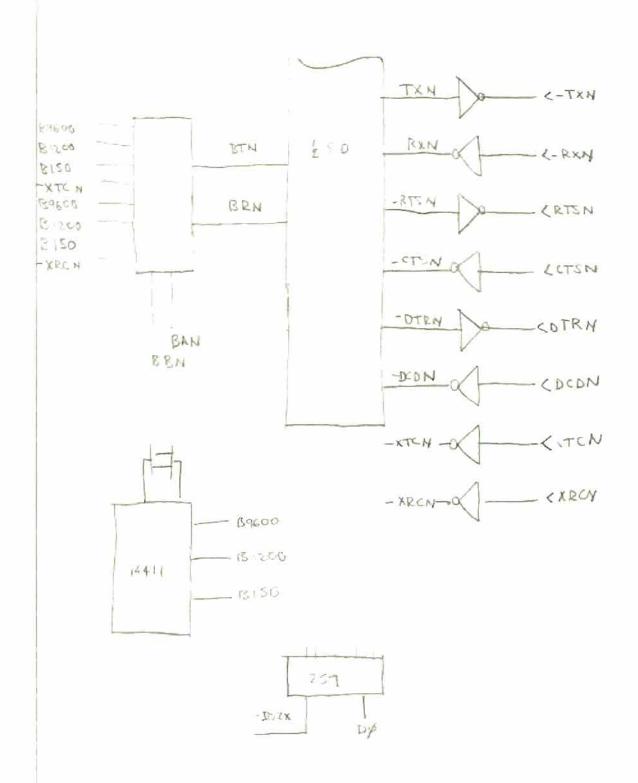

#### 4.2. Dedicated Rost

The dedicated host is the interface between the general purpose host computers and the array. The dedicated host interfaces to the array

through one asynchronous connection and is the master of the control bus.

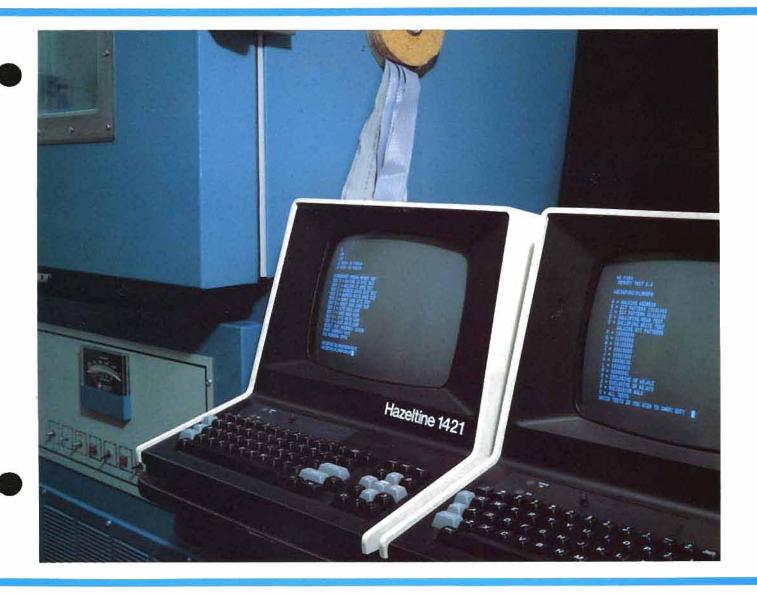

The dedicated host also interfaces to the mainframe hosts and to consterminals.

In addition to serving as a hardware interface to the array, the dedicated host fulfills an important function in some algorithms, see [HEP 81]. For this reason, the dedicated host will have a substantial amount of RAM: 512Kb-1Mb.

An unsuspected function of the dedicated host is the running of diagnostics on the entire array. The dedicated host will have the ability to control the supply voltage and clock frequency as well as control the master reset and RAM refresh rate of the entire array. These abilities will aid diagnostic programs in locating faulty boards.

The present plans are to construct the dedicated host with the same as the main processors, for reasons of software compatibility. Future plans may call for more than one dedicated host, or a processor that is faster than the main processors.

#### 4.3. Mainframe Hosts

Since neither the array nor the dedicated host will have any secondary storage, they would be inappropriate for compilers. Compiling will occur on either the HEP VAX or the CS DEC-20 and the machine code will be downloaded to the dedicated host and then to the array. At present it appears that the CS DEC-20 will be used for assembly level system software developement and the HEP VAX will be used for applications programming in C.

#### 5. Proposed Plan of Action

A project to evaluate this architecture will consist of three phases:

- 1. Construction of a 64 processor prototype array and dedicated host.

- 2. Development of system software.

- 3. Application of the machine to different problems.

- 4. Construction of a 1024 processor hypercube machine.

This document will be concerned only with items 1,2, and 4. Caltech's High Energy Physics group is eager to apply such a machine to real physics problems [HEP 81].

#### 5.1. Current Status

Work has already begun on constructing the hypercube machine. Funds were provided in anticipation in the computer science ARPA budget for work on building a concurrent machine. These funds, amounting to a non-renewable \$20,000, are being used at present. ARPA interest in the project is considerable, but in a general atmosphere of budget cutting, funds to construct a useful hypercube machine will be difficult to obtain. Additional funding is being persued with ARPA as well as with others.

As of January 1982 approximately 50% of the engineering has been completed. Engineering is proceeding on the remainder of the machine and will be completed before any additional funding could have an effect.

#### 5.2. Timetable for Future Work

The only part of the machine that has not yet been funded is the

construction of the actual array. A proposed timetable for future work is shown below:

#### Phase I - 64 processor machine

#### 1 September 1981

5

Project to build 64 processor test model of the hypercube machine begins. Hardware design and prototyping begins immediately.

- 1 January 1982 Working model of the main processor. Software development begins now.

- l March 1982 Design of main processor is complete and the design is submitted to a contractor for PC layout and fabrication of 64 units. A complete software model of the hypercube machine is complete, including the dedicated host and at least two main processors.

- 1 July 1982 Primitive system software is completed. Boards to construct a 64 processor array are delivered by the contractor. Boards are now assembled into an array and tested.

- 1 October 1982 64 processor system is fully operational. Programs of the approximate complexity of Laplace's equation run. A technology evaluation is performed to determine if better chips are available for any part of the system. If necessary, redesign begins.

#### Phase II - 1024 processor machine

- 1 March 1983 A potentially redesigned main processor is submitted to a contractor for construction of 1024 units. Some physics research problems should be complete by this time.

- 1 October 1983 1024 unit hypercube machine becomes fully operational.

Other parts of the machine are used only in quantity one, and engineering prototypes will be used.

#### 5.3. Cost Estimates

An estimate of the cost of constructing one hypercube machine processor and building it into a processor array is shown in figure 2.

It will be noted that in figure 2 the cost is largely influenced by the \$400.00 cost of the 8087 floating point chip. As of January 1982 the 8087 chips are scheduled for delivery to suppliers on a 4-6 week basis at a retail cost of \$400. It is expected that the price of these chips will drop very significantly in the following few months.

Besides the 8087, the price of other parts is dropping rapidly now. In particular, the 8086 processor and the 64K RAM chips should be available for less than the proposed price. Figure 3 is a prediction of the actual cost of producing the array on a per unit basis. These figures only are used in the later cost estimates.

Figure 4 is a schedule of the expenses that would be required to complete the project if funding were available.

Considerable graduate student and faculty interest has been expressed in the Computer Science Department in communications software for the hypercube machine. Funding of research in this topic can proceed after the machine is in operation. To get the machine into a basic operation it will be necessary to have a primitive network operating system and diagnostics. A manpower budget for this is included in figure 4.

| Item                       | Quantity       | Cost      | Extension |

|----------------------------|----------------|-----------|-----------|

| Double sided PC board:     | $\overline{1}$ | \$50.00   | \$50      |

| 8087 floating point:       | 1              | \$400.00  | \$400.00  |

| 8086 microprocessor:       | 1              | \$100.00  | \$100.00  |

| 64K RAM (2164):            | 16             | \$14.00   | \$224.00  |

| 8529A interrupt:           | 2              | \$18.00   | \$36.00   |

| 74S225 fifo:               | 1 2            | \$4.50    | \$54.00   |

| misc IC:                   | many           | \$40.00   | \$40.00   |

| Share power supply (2A/5V) | 1/10th         | \$300.00  | \$30.00   |

| Share backplane            | 1/64th         | \$4000.00 | \$63.00   |

| sub-total:                 |                |           | \$997.00  |

| Assembly and testing:      |                | \$250.00  | \$250.00  |

| total:                     |                |           | \$1247.00 |

Figure 2: Per Processor Costs

| March | 1982 | \$1200 |

|-------|------|--------|

| March | 1983 | \$800  |

Figure 3: Estimated Cost of the Main Processor on a Per Unit Basis

|                                | 1-Mar-82- | 1-0ct-82- | 1-Mar-83- |  |  |  |

|--------------------------------|-----------|-----------|-----------|--|--|--|

|                                | 30-Sep-82 | 28-Feb-83 | 1-0ct-83  |  |  |  |

|                                |           |           |           |  |  |  |

| 64 processor prototype:        | \$76,800  |           |           |  |  |  |

| (64 processors at \$1200 each) |           |           |           |  |  |  |

| 1023 processor array:          |           |           | \$819,000 |  |  |  |

| (1024 processors at \$         | 800 each) |           |           |  |  |  |

| Staff (quantity):              |           |           |           |  |  |  |

| DeBenedictis                   | 1         | 1         | 1         |  |  |  |

| Graduate Student:              |           |           |           |  |  |  |

| Hardware work:                 | 1         | 0         | 1         |  |  |  |

| Software work:                 | 3         | 4         | 3         |  |  |  |

| Technical:                     |           |           | `         |  |  |  |

| Hardware work:                 | 1         | 1         | 4         |  |  |  |

| Software work:                 | 1         | 0         | 0         |  |  |  |

Period

Figure 4: Expense Schedule for Construction of the Hypercube Machine

#### HOMOGENEOUS MACHINE

Figure 5: An Overview of the Hypercube Machine

17

#### REFERENCES

- [Browning 80] Sally Browning, <u>The Tree Machine: A Highly Concurrent</u>

Computing Environment, Ph.D. thesis, California Institute of Technology, 1980.

- [HEP 81] Brooks, E., Fox, G., Gupta, R., Martin, O., Otto, S.,

DeBenedictis, E., Nearest Neighbor Concurrent Processor, Caltech High

Energy Physics, Technical Report, 1981.

- [Kung 80] Mead, C., Conway, L., <u>Introduction to VLSI Systems</u>, Addison-Weseley pp. 271-292, chapter 8.3, 1980. Section contributed by H. T. Kung and Charles E. Leiserson

- [Locanthi 80] Bart Locanthi, The Homogeneous Machine, Ph.D. thesis, California Institute of Technology, 1980.

- [Seitz 81] Chuck Seitz, Ensemble Architectures for VLSI -- A Survey and Taxonomy. Attached.

## A Communications Operating System for the Homogeneous Machine

13 January 1982

Erik DeBenedictis

Copyright (C) 1982 Caltech. Copying is allowed.

The research described in this document was sponsored by the Defense Advanced Besearch Projects Agency, ARPA Order number 3771, and monitored by the Office of Naval Research under contract number N00014-79-C-0597.

115. 4707

This in an internal working document of the Caltech Computer Science Department. Some of the ideas expressed in this document may be only partially developed or erroneous. All of the materials included are the property of Caltech and its sponsors. Distribution of this document outside the immediate working community is discouraged; publication of this document is forbidden.

#### 1. Introduction

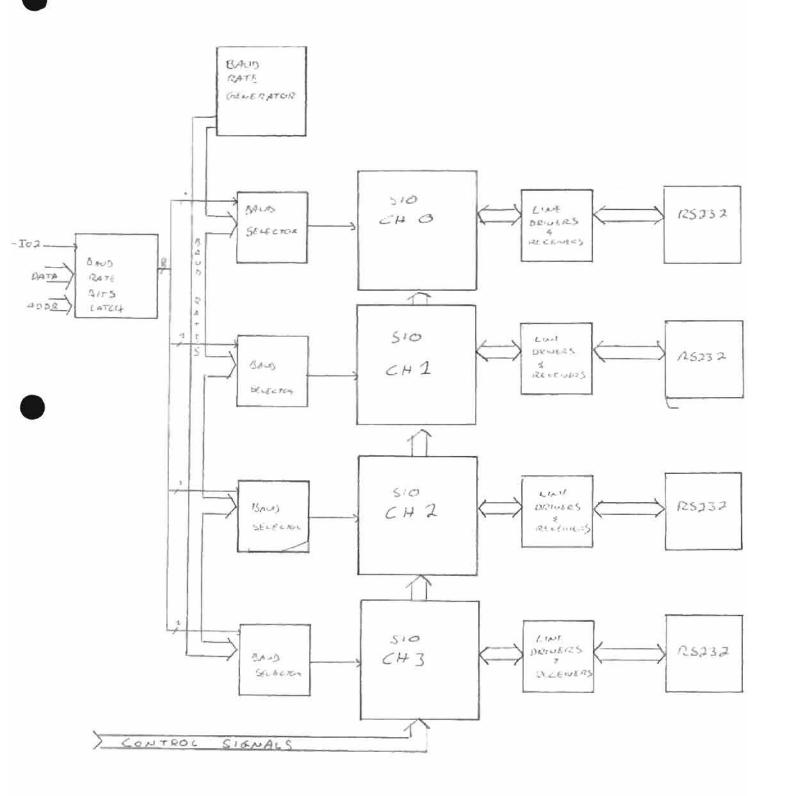

What communications primitives will be available to programs running on the homogeneous machine? One requirement is that the CPU overhead be low when the communications is simple (e.g. systolic). On the other hand, the communications must be general enough to support dynamically allocated processes (e.g. COPE). If a general communications strategy existed that was computable with these requirements it could be implemented as part of the ROM resident operating system.

#### 2. Types of Problems and Necessary Communications Capabilities

A spectrum of communications strategies have been proposed. Each strategy trades simplicity and efficiency for capability. These are listed below:

Systolic:

In systolic communication both the sender and the receiver must be waiting on the same communication event for the event to proceed. Systolic communication is modeled by two monitor calls; one to send a message over a particular cliamnel, and one to receive a message. The characteristics of the calls is that they hang until function can be completed. locking out any other processor activity. No interrupts are required.

Processor Directed: In processor directed communication each message is accompanied by a specification of the processor that is to receive it. When a message enters a processor that message is either delivered to the program running in that processor or relayed to another processor. If relaying must occur the operating system decides which link is most appropriate to forward the message. Queueing can be implemented for relayed messages and/or for messages dustined for the processor. Interrupts are required.

**Process Directed:**

In process directed communication there may be more than one process in each processor. Furthermore, processes may move around between processors. Communication is directed to a particular process, even though the processor where that

process is currently resident may not be known. Implementation of this scheme is very involved.

#### 3. Processor Directed Communication

Processor directed communication offers extremely high speed and sufficient generality to be the best choice. The communications primatives appropriate for this type of communication are shown below:

Int outA(Dest) Specifies a message to another processor. Dest is the destination processor (0-63).

int outB(Buf,Len) Sends message data to the selected processor. Buf is pointed to an integer array that contains the information to be transmitted. Len bytes starting at Buf are transmitted. The value returned is 0 if the transmission was successful or -1 if output buffer space was full.

int inA()

Receives a message. The value returned is the identification of the sending processor, or -1 if no message was available.

int inB(Buf,Len) Receives a message. Buf is a pointer to a Len word block where the message is deposited. If the remaining message is longer than the buffer, the buffer is filled with as much of the message as possible and 0 is returned. If the message fits in the buffer, the number of bytes transferred is returned.

#### 4. Deadlock

Deadlock can potentially occur for two reasons: 1) the user program assumes too much queueing, or 2) the message passing system deadlocks. The following rule will prevent a user program from deadlocking:

User program deadlock prevention rule:

A user program may not wait on a failed out call unless in calls are processed during the wait.

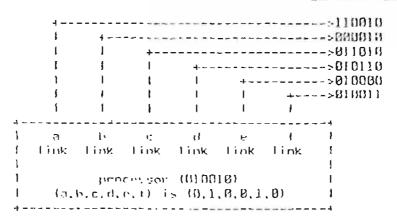

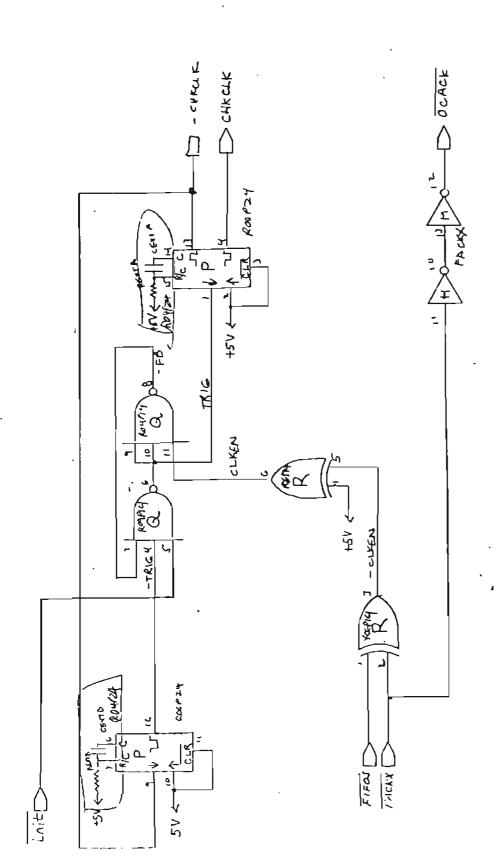

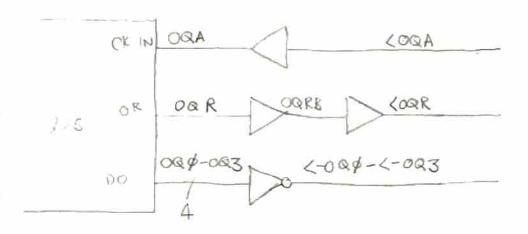

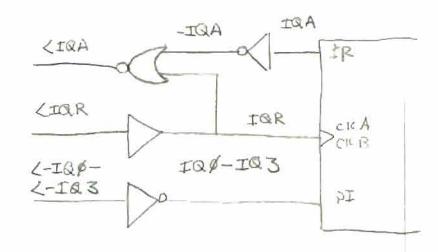

The message passing system uses a deadlock free routing algorithm. This algorithm is described below (refer to figure 1 for notation):

Figure 1: Notation Concerning Processors in a Hypercube

- Let processors be identified by their coordinate in the hypercober (a.b.c.d.e.f). The letters a.b.c.d.e.f are either zero or one, and are transmitted as a binary number abodef.

- Let the links to other processors he labeled a, b, c, d, e, and f. The labeling is chosen to correspond to the bit labeling of the previous paragraph. (I.e. the processors on either end of link c have identifications that differ only in the c bit.)

- When a message is available from a link the identification of its

destination processor is analyzed before it is removed from the input

queue. Analysis consists of XORing the destination processor

identification with the identification of the processor with the

message and performing one of two functions:

- 1. If the identifications are the same then the message is destined for that processor. The message is made available for input. If the input buffer is full, the operating system runs the user program until that is no longer so.

- 2. If the identifications are different then the message must be forwarded. The link to forward is determined by the following algorithm: the leftmost bit in the difference is located and that determines the forwarding link,

This system does not deadlock for the following reason: If a message actives on

link f (least significant bit) then it must be destined for that processor. This is true because to be forwarded to link f by the previous processor all other bits must match. The user program on the processor must remove the message eventually. The system therefore cannot deadlock with messages in link f.

Now consider link e. If a message has arrived in link e, bits are must match. If bit f matches then the message can be made available for input and time is no problem. If bit f does not match the message is forwarded to link f. Since the system cannot deadlock with a message in link f, it will not deadlock in this condition. Therefore the system will not deadlock with a message in link e or f.

By induction, it has been proven that all links to the right of link x do x, deadlock. If a message arrives on link x then it is known that all bits to the left and including x match. Therefore the message will either match exactly, or it will be forwarded to a link to the right of x. If an exact match occurs, the message is consumed by the user program. If the message is forwarded deadlock country occur because all links to the right of x do not deadlock. Therefore, link x does not deadlock.

rain

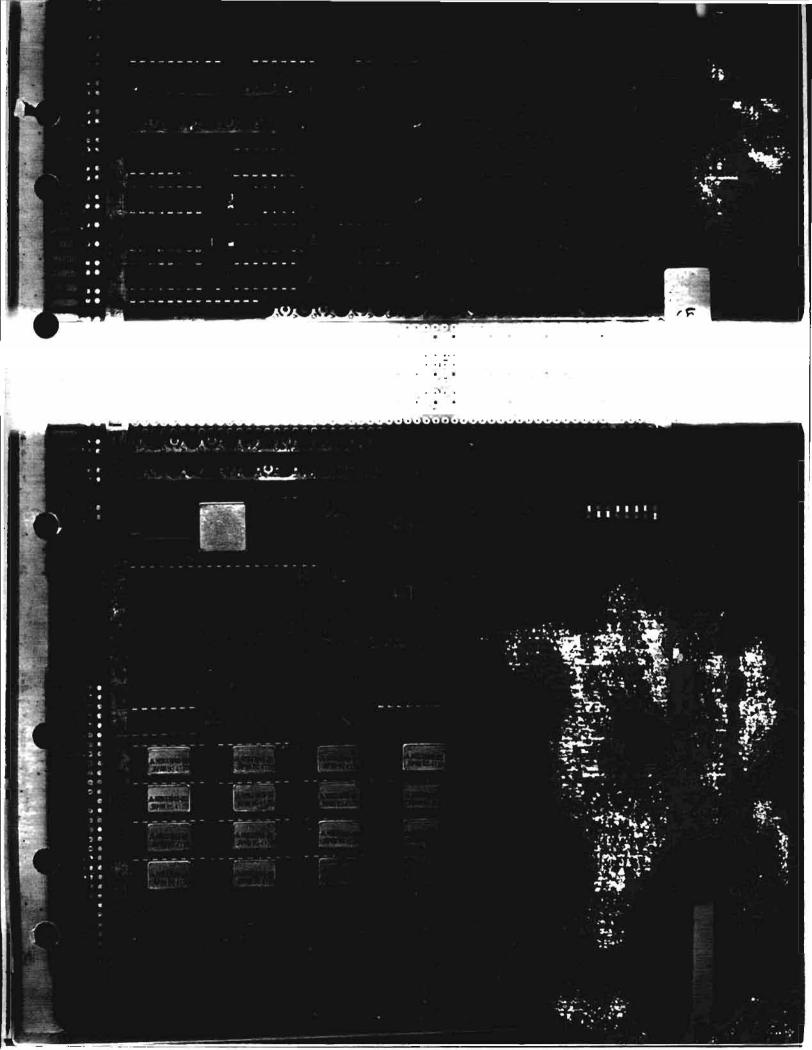

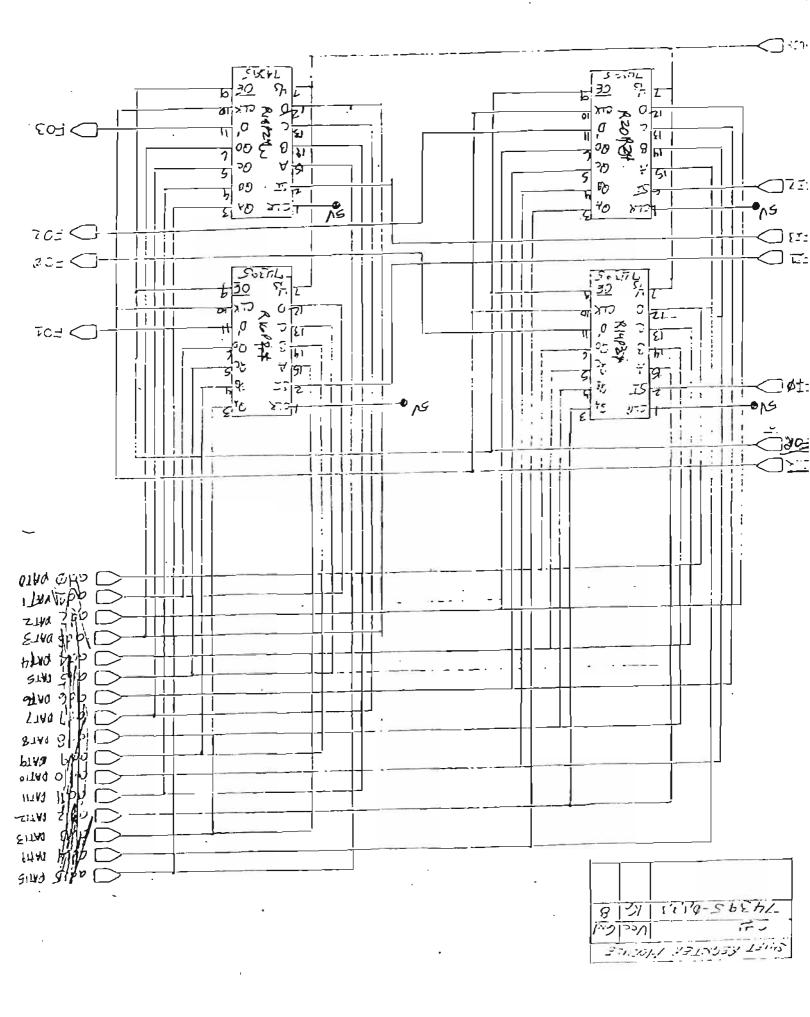

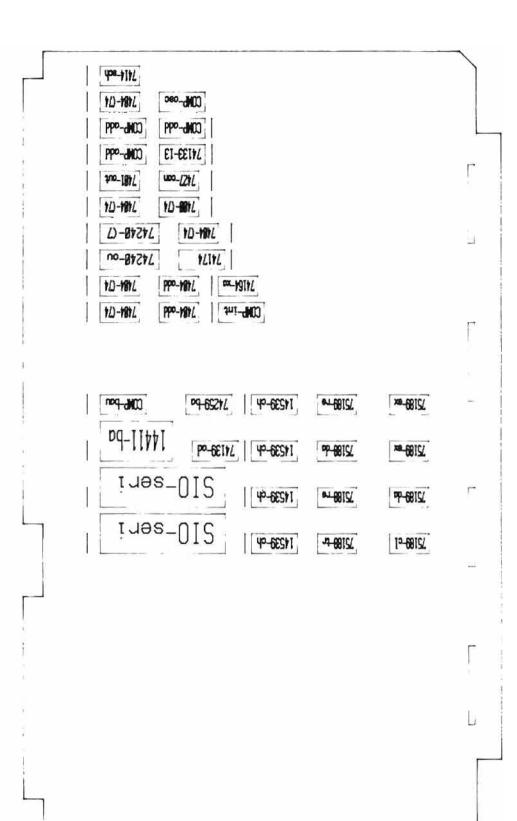

14001-8 14001-2 7414-81 7464-81 14001-1 74225-1 74225-2 74225-B 74941-B 74941-2 74225-1 74941-1 74225-0 2164-ram 74109-pa 74280-hi 2164-ram 7432-mi 2164-ram 2164-ram 7400-mem 2164-ram 2164-ram 2164-ram 2164-ram 2164-ram 7465-par 74373-ac 74244-bu 74373-hi 2164-ram 2164-ram 74288-10 2164-ram 2164-ram 7404-7804 74373-10 8288-bus 2164-ram 2164-ram 2164-ram 2164-ram 2164-ram

8086-pro

2-414/

74225-2

8087-mat

| 8087-mat                  |                         |  |

|---------------------------|-------------------------|--|

| 2532-hig 2532-low         | 74225-3 7484-23         |  |

| 8259A-s1 8259A-ma         | 74941-3                 |  |

| 74138 ma 7492 sto 74395-9 | 74225-3 14001-3         |  |

| 74138 wr 74174-st 74395-1 | 74225-4 14001-4 74941-4 |  |

| 74138-re 74288-st 74395-2 | 74225-4 7414-45         |  |

| 74174-ac 7485-aps 74395-3 |                         |  |

|                           | 74225-5 7484-45 74941-5 |  |

|                           | 74225-5 14001-5         |  |

12 chur may (6) VCC GND no numeric first no NC - just delete. pin #'s UXX - \$4

National Technology

Senta Ana.

muss proct of multilager ~ 8 mil.

## PROM / ADDRESS

### ACCESSORIES 74367 ADII < ADIO < CGLD02 AD9 CGLOD1 - KGLOD 9 SOA -EXTIN -RESET RESET --CLR GLOCE Di AD8 D Do -><GLOCØ GLOC 1 AD9 > De Do >GLOCI 74174 SLOCZ ×GIOC2 ADIO > Do GLOC3 Do > < GLOC 3 DE ADII > G-10C4 DL >-CLRPTY ADI2 Do -LED LED Di ADB > Do - EXTO UT

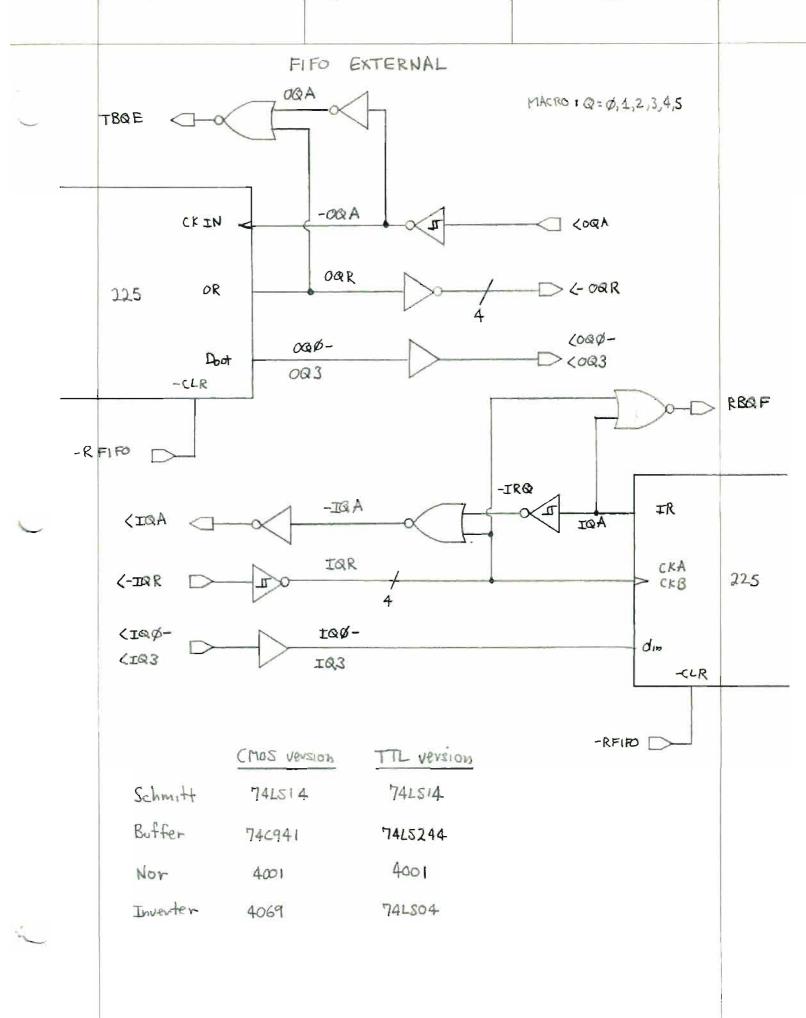

FIFO 4-16-4 conventer

## State Machine

| CONTROL                                      | Bus      | ASYNC               |

|----------------------------------------------|----------|---------------------|

| CLK                                          | GND      | <0Q\$               |

| RESET                                        | GND      | <0Q2                |

| INN                                          | GND      | - GND               |

| NC                                           | GND      |                     |

| (GLODA                                       | GND      |                     |

| <6L001                                       | GND      | GND                 |

| (GLODZ                                       | GND      | ARIL                |

|                                              | CND      | < IQ3               |

| < NC                                         | 1771 815 | <iq1< td=""></iq1<> |

| < GLOC Ø                                     | GND      |                     |

| < GLOC1                                      | CIND     |                     |

| < GLOCZ                                      | GND      |                     |

| <gloc3< td=""><td>GND</td><td></td></gloc3<> | GND      |                     |

| CGLOC 4                                      | GND      |                     |

| < NC                                         | GND      |                     |

| NC ',                                        |          |                     |

CABLE

<001

(003

< 002A

GND

GND

SDIY

CIRCO

/ LIGR

| Total   72844   787-pc   2164-va   2 | 28 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2164-re 2164-r |         |                     |                      |          |         |         |         |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------|----------------------|----------|---------|---------|---------|---------|

| 2164-va 7487-va 2164-va 2164-v | 2164-ve 7487-ve 2164-ve 2164-v | 2164-va 2164-v | 7238-Io | 2164-res            | 2164-res<br>2164-res | 2184-ras | 784-m   | 388-bus | 010     | nat.    |

| 2164-ve 2164-v | 2164-ve 2164-v | 2164-va 2164-v |         | 7407-per<br>164-res | 164-re               | 184-ra   |         |         | 786-F   | 787-    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-78 2184-7 | 28 Hr   |                     |                      | -        | 74373-0 | 74244-b | <u></u> | <u></u> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                     |                      |          | I j     | 2       | 6-low   | Fhin    |

8259A-s1

7427-ets 74288-et 7455-eps

74365-8 74365-2 74365-3

784-29 1881-3 1881-3 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 1881-5 18

7425-3 7425-3 7425-4 7425-4 7425-5 7425-5

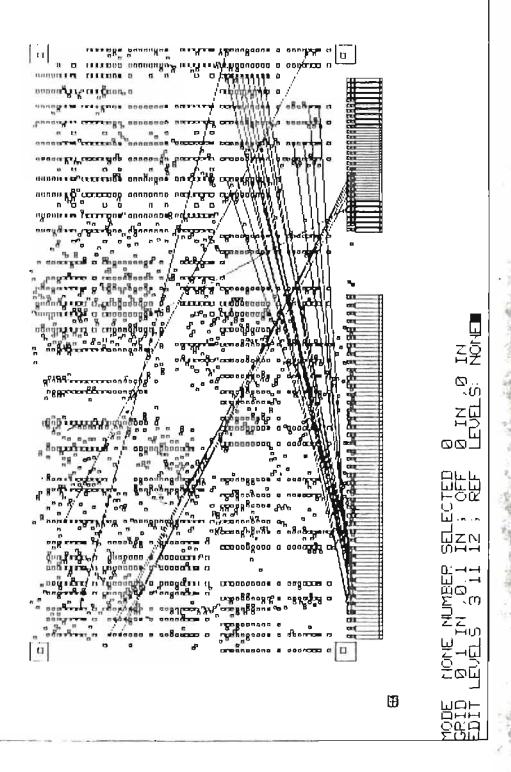

# Jeffery Cavallaro

Thu Apr 22 17:47:19 1982

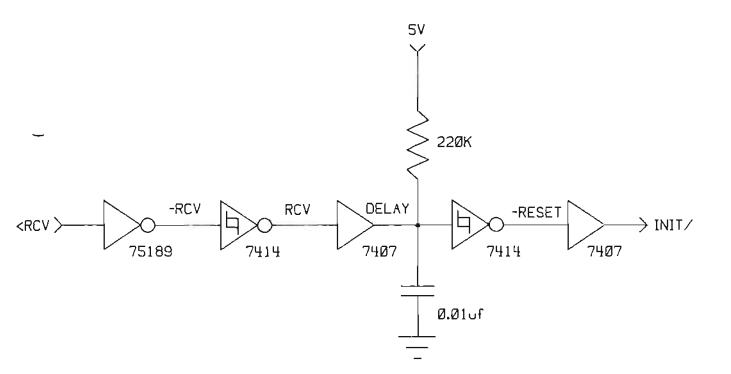

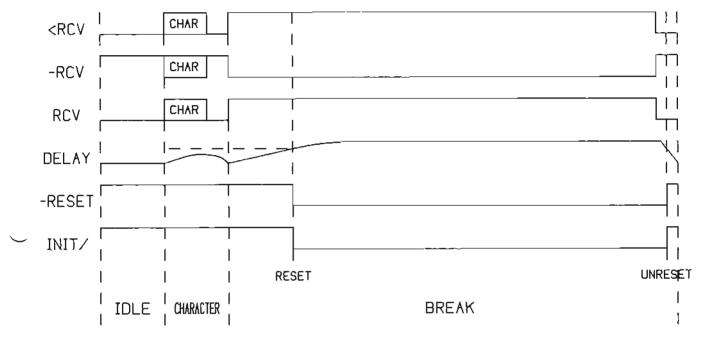

kreak.chp

**R42+13 PINS**

54

: GND

### Sorted List: X: 0.00 Y: 0.00 +5/GND 01 PINS :5V X: 0.10 Y: 0.00 +5/GND +5/GND R03+01 PINS 2 : GND X: 0.50 Y: 0.00 **RØ5+Ø1 PINS** 3 :50 +5/GND X: 0.90 Y: 0.00 4 R07+01 PINS : GND +5/GND X: 1.30 Y: 0.00 R09+01 PINS 5 :5V X: 1.70 Y: 0.00 +5/GND R11+01 PINS X: 2.10 Y: 0.00 6 : GND +5/GND R13+01 PINS 7 :50 X: 2.50 Y: 0.00 +5/GND R15+01 PINS В : GND +5/GND X: 2.90 Y: 0.00 R17+01 PINS 9 :5U +5/GND X: 3.30 Y: 0.00 R19+01 PINS X: 3.70 Y: 0.00 10 : GND +5/GND R21+01 PINS 11 ; 5U X: 4.10 Y: 0.00 +5/GND R22+01 PINS 12 : GND +5/GND X: 4,40 Y: 0.00 R24+01 PINS 13 : 5U +5/GND X: 4.80 Y: 0.00 R25+01 PINS 14 : GND X: 5.10 Y: 0.00 +5/GND R27+01 PINS 15 :50 +5/GND X: 5.50 Y; 0.00 R28+01 PINS X: 5.80 Y: 0.00 16 : GND +5/GND 2414 10+0ER 17 X: 6.20 Y: 0.00 :50 +5/GND R31+01 PINS 10 : GND X: 6.50 Y: 0.00 +5/GND R33+01 PIN5 19 : 5V X: 6.90 Y: 0.00 +5/GND R34+01 PINS 20 : GND +5/GND X: 7.20 Y: 0.00 :50 R36+01 PINS 21 +5/GND X: 7.60 Y: 0.00 R38+01 PINS 22 : GND X: 8.00 Y: 0.00 +5/GND R40+01 PINS 23 ;5V X: 8.40 Y: 0.00 +5/GND R42+01 PINS 24 ; GND +5/GND X: 8.80 Y: 0.00 R44+01 PINS 25 :5U +5/GND X: 9.20 Y: 0.00 R4 01 PINS 26 X: 9.60 Y: 0.00 : GND +5/GND R48+01 PINS 27 :5V +5/GND X:10.00 Y: 0.00 28 R50+01 PINS : GND +5/GND X:10,40 Y: 0.00 R52+01 PINS 29 :50 +5/GND X:10.80 Y: 0.00 R54+01 PINS 30 : GND +5/GND X:11,20 Y' 0,00 **RØ1+13 PINS** 31 :5U +5/GND X: 0.10 Y: -1.20 **R03+13 PINS** 32 : GND X: 0.50 Y:-1.20 +5/GND X: 0.90 Y:-1.20 R05+13 PINS :50 33 +5/GND **R07+13 PINS** 34 ; GND +5/GND X: 1.30 Y:-1.20 R09+13 PINS 35 : 5V +5/GND X: 1.70 Y:-1.20 R11+13 PINS X: 2.10 Y:-1.20 36 : GND +5/GND R13+13 PINS 37 :5V X: 2.50 Y;-1.20 +5/GND R15+13 PINS 38 X: 2.90 Y;-1.20 : GND +5/GND R17+13 PINS 39 :50 +5/GND X: 3.30 Y:-1.20 X: 3.70 Y:-1,20 R19+13 PINS 40 : GND +5/GND R21+13 PINS 41 :50 X: 4.10 Y:-1.20 +5/GND R22+13 PINS 42 : GND X: 4.40 Y:-1.20 +5/GND R24+13 PINS 43 :50 X: 4.80 Y:-1.20 +5/GND X: 5.10 Y:-1.20 R25+13 PINS 44 : GND +5/GND 45 X: 5.50 Y:-1.20 R27+13 PINS :5⊍ +5/GND R28+13 PINS 46 : GND X: 5.80 Y:-1.20 +5/GND 47 :50 X: 6.20 Y:-1.20 R30+13 PINS +5/GND R31+13 PINS 48 X: 6.50 Y:-1.20 : GND +5/GND X: 6,90 Y:-1.20 R33+13 PINS 49 :5V +5/GND X: 7.20 Y:-1.20 **R34+13 PINS** 50 : GND +5/GND R3413 PINS 51 :5U +5/GND X: 7.50 Y:-1.20 R3 13 PINS 52 : GND +5/GND X: 8.00 Y:-1.20 R40+13 PINS 53 : 5V +5/GND X: 8.40 Y:-1.20

+5/GND

X; 8.80 Y;-1.20

| R44+13  | PINS | 55  | :50   | +5/GND | X: 9.20 Y:-1.20 |

|---------|------|-----|-------|--------|-----------------|

| R4 13   | PINS | 56  | GND   | +5/GND | X: 9.60 Y:-1.20 |

| R45+13  | PINS | 57  | :50   | +5/GND | X:10.00 Y:-1.20 |

| R50+13  | PINS | 58  | : GND | +5/GND | X:10.40 Y:-1.20 |

| R52+13  | PINS | 59  | : 50  | +5/GND | X:10.80 Y:-1.20 |

| R54+13  | PINS | 60  | : GND | +5/GND | X:11.20 Y:-1.20 |

| RØ1+25  | PINS | 51  | :50   | +5/GND | X: 0.10 Y:-2.40 |

| RØ3+25  | PINS | 62  | ; GND | +5/GND | X: 0.50 Y:-2.40 |

| RØ5+25  | PINS | 63  | :50   | +5/GND | X: 0.90 Y:-2.40 |

| RØ7+25  | PINS | 64  | : GND | +5/GND | X: 1.30 Y:-2.40 |

| RØ9+25  | PINS | 65  | :50   | +5/GND | X: 1.78 Y:-2.40 |

| R11+25  | PINS | 66  | : GND | +5/GND | X: 2.10 Y:-2.40 |

| R13+25  |      | 67  | :50   | +5/GND | X: 2.58 Y:-2.40 |

| R15+25  |      | 68  | : GND | +5/GND | X: 2.90 Y:-2.40 |

| R17+25  |      | 69  | :50   | +5/GND | X: 3.30 Y:-2.40 |

| R19+25  |      | 70  | GND   | +5/GND | X: 3.70 Y:-2.40 |

| R21+25  |      | 71  | :\$0  | +5/GND | X: 4.10 Y:-2.40 |

| R22+25  |      | 72  | : GND | +5/GND | X: 4.40 Y:-2.40 |

| R24+25  |      | 73  | :5U   | +5/GND | X: 4.80 Y:-2.40 |

| R25+25  |      | 74  | : GND | +5/GND | X: 5.10 Y:-2.40 |

| R27+25  |      | 75  | :50   | +5/GND | X: 5.50 Y:-2.40 |

| R28+25  |      | 76  | : GND | +5/GND | X: 5.80 Y:-2.40 |

| R30+25  |      | 77  | :50   | +5/GND | X: 6.20 Y:-2.40 |

| R31+25  |      | 78  | : GND | +5/GND | X: 6.50 Y:-2.40 |

| R31+25  |      | 79  | :50   | +5/GND | X: 6.90 Y:-2.40 |

| R34+25  |      | 80  | GND   | +5/GND | X: 7.20 Y:-2.40 |

| R35±25  |      | 81  | :50   | +5/GND | X: 7.60 Y:-2.40 |

| RE 25   |      | 82  | : GND |        |                 |

| R40+25  |      |     |       | +5/GND | X: 8.00 Y:-2.40 |

|         |      | 83  | :50   | +5/GND | X: 8.40 Y:-2.40 |

| R42+25  |      | 84  | : GND | +5/GND | X: 8.80 Y:-2,40 |

| R44+25  |      | 85  | : 5U  | +5/GND | X: 9.20 Y:-2.40 |

| R46+25  |      | 86  | : GND | +5/GND | X: 9.60 Y:-2.40 |

| R48+25  |      | 87  | :50   | +5/GND | X:10.00 Y:-2.40 |

| R50+25  |      | 88  | : GND | +5/GND | X:10.40 Y:-2.40 |

| R52+25  |      | 89  | :50   | +5/GND | X:10.80 Y:-2.40 |

| R54+25  |      | 90  | : GND | +5/GND | X:11.20 Y:-2.40 |

| RØ1+37  |      | 91  | :50   | +5/GND | X: 0.10 Y:-3.60 |

| RØ3+37  |      | 92  | GND   | +5/GND | X: 0.50 Y:-3.60 |

| RØ5+37  |      | 93  | :50   | +5/GND | X: 0.90 Y:-3.60 |

| RØ7+37  |      | 94  | : GND | +5/GND | X: 1.30 Y:-3.60 |

| RØ9+37  |      | 95  | : 50  | +5/GND | X: 1.70 Y:-3.60 |

| R11+37  |      | 96  | : GND | +5/GND | X: 2.10 Y:-3.60 |

| R13+37  |      | 97  | :50   | +5/GND | X: 2.50 Y:-3.60 |

| R15+37  |      | 98  | : GND | +5/GND | X: 2.90 Y:-3.60 |

| R17+37  |      | 93  | :50   | +5/GND | X: 3.30 Y:-3.60 |

| R19+37  |      | 100 | : GND | +5/GND | X: 3.70 Y:-3.60 |

| R21+37  |      | 101 | : 50  | +5/GND | X: 4.10 Y:-3.60 |

| R22+37  |      | 102 | GND   | +5/GND | X: 4.40 Y:-3.60 |

| R24+37  |      | 103 | :50   | +5/GND | X: 4.80 Y:-3.60 |

| R25+37  |      | 104 | : GND | +5/GND | X: 5.10 Y:-3.60 |

| R27+37  |      | 105 | : 50  | +5/GND | X: 5.50 Y:-3.60 |

| R28+37  |      | 106 | : GND | +5/GND | X: 5.80 Y:-3.60 |

| R37 37  |      | 107 | :50   | +5/GND | X: 6.20 Y:-3.60 |

| R3 ■ 37 |      | 108 | GND   | +5/GND | X: 6.50 Y:-3.60 |

| R33+37  |      | 109 | : 50  | +5/GND | X: 6.90 Y:-3.60 |

| R34+37  | PINS | 110 | : GND | +5/GND | X: 7.20 Y:-3.60 |

| 1000    |      |     |       |        |                 |

| R36+37          | PINS | 111  | :50   | +5/GND | х:         | 7.60 | Y:-3.60  |

|-----------------|------|------|-------|--------|------------|------|----------|

| R2 37           | PINS | 112  | : GND | +5/GND | X:         | 8.00 | 93.E-:Y  |

| R4-37           | PINS | 113  | :50   | +5/GND | X:         | 8.40 | 03.E-:Y  |

| R42+37          | PINS | 114  | GND   | +5/GND | X:         | 8.80 | Y:-3.60  |

| R44+37          | PINS | 115  | :50   | +5/GND | X:         | 9.20 | Y:-3.60  |

| R46+37          | PINS | 116  | : GND | +5/GND | X:         | 9.60 | Y:-3.60  |

| R48+37          | PINS | 117  | :50   | +5/GND | X:1        | 0.00 | Y:-3.60  |

| R5Ø+37          | PINS | 118  | : GND | +5/GND |            |      | Y:-3.60  |

| R52+37          | PINS | 119  | :50   | +5/GND |            |      | Y:~3.60  |

| R54+37          | PINS | 120  | ; GND | +5/GND |            |      | Y:-3.60  |

| RØ1+49          | PINS | 121  | :50   | +5/GND |            |      | Y:-4.80  |

| R <b>0</b> 3+49 | PIN5 | 122  | : GND | +5/GND |            |      | Y:-4.80  |

| RØ5+49          | PINS | 123  | : 50  | +5/GND | X:         |      | Y:-4.80  |

| RØ7+49          | PINS | 124  | : GND | +5/GND | X:         |      | Y:-4.80  |

| RØ9+49          | PINS | 125  | : 50  | +5/GND | X:         |      | Y:-4.80  |

| R11+49          | PINS | 126  | : GND | +5/GND |            |      | Y:-4.80  |

| R13+49          | PINS | 127  | : 50  | +5/GND | X:         |      | Y:-4.80  |

| R15+49          | PINS | 128  | GND   | +5/GND | X:         |      | Y:-4.80  |

| R17+49          | PINS | 129  | :50   | +5/GND | <b>X</b> : |      | Y:-4.80  |

| R19+49          | PINS | 130  | GND   | +5/GND | X:         |      | Y:-4.80  |

| R21+49          | PINS | 131  | :50   | +5/GND | <b>X</b> : |      | Y:-4.80  |

| R22+49          | PINS | 132  | : GND | +5/GND | X:         |      | Y:-4.80  |

| R24+49          | PINS | EE 1 | :50   | +5/GND | X:         |      | Y:-4.80  |

| R25+49          |      | 134  | : GND | +5/GND | <b>x</b> : |      | Y:-4.80  |

| R27+49          |      | 135  | : 5V  | +5/GND | X:         |      | Y:-4.80  |

| R28+49          |      | 136  | : GND | +5/GND | Χï         |      | Y:-4.80  |

| R30+49          |      | 137  | :50   | +5/GND | X:         |      | Y:-4.80  |

| R3 49           |      | 138  | ; GND | +5/GND | X:         |      | Y:-4.80  |

| R33749          |      | 199  | : 50  | +5/GND | X:         |      | Y:-4.80  |

| R34+49          |      | 140  | : GND | +5/GND | X÷         |      | Y:-4.80  |

| R36+49          |      | 141  | : 50  | +5/GND | X          |      | Y: ~4.80 |

| R38+49          |      | 142  | : GND | +5/GND | X :        |      | Y:-4.80  |

| R40+49          |      | 143  | :50   | +5/GND | X          |      | Y:-4.80  |

| R42+49          |      | 144  | : GND | +5/GND | X:         |      | Y:-4.80  |

| R44+49          |      | 145  | : 50  | +5/GND | X:         |      | Y:-4.80  |

| R46+49          |      | 146  | : GND | +5/GND | X:         |      | Y:-4.80  |

| R48+49          |      | 147  | : 50  | +5/GND |            |      | Y:-4.80  |

| R50+49          |      | 148  | : GND | +5/GND |            |      | Y:-4.80  |

| R52+49          |      | 149  | :50   | +5/GND |            |      | Y:-4.80  |

| R54+49          |      | 150  | : GND | +5/GND |            |      | Y:-4.80  |

| RØ1+Ø7          |      | 151  | : GND | +5/GND |            |      | Y:-0.60  |

| RØ3+Ø7          |      | 152  | :50   | +5/GND | X:         |      | Y:-0.60  |

| RØ5+07          |      | 153  | GND   | +5/GND | X:         |      | Y:-0.50  |

| RØ7+07          |      | 154  | :50   | +5/GND |            |      | Y:-0.50  |

| R09+07          |      | 155  | : GND | +5/GND | X:         |      | Y:-0.60  |

| R11+07          |      | 156  | :50   | +5/GND | X:         |      | Y:-0.60  |

| R13+07          |      | 157  | GND   | +5/GND | X:         |      | Y:-0.60  |

| R15+07          |      | 158  | :50   | +5/GND | X:         |      | Y:-0.60  |

| R17+07          |      | 159  | GND   | +5/GND | X:         |      | Y:-0.60  |

| R19+07          |      | 160  | :50   | +5/GND | X:         |      | Y:-0.60  |

| R21+07          |      | 161  | GND   | +5/GND | X:         |      | Y:-0.60  |

| R22+07          |      | 162  | :50   | +5/GND |            |      | Y:-0.60  |

| R24407          |      | 163  | GND   | +5/GND |            |      | Y:-0.60  |

| R2 37           |      | 164  | :50   | +5/GND | X;         |      | Y:-0.60  |

| R27+07          |      | 165  | GND   | +5/GND |            |      | Y:-0.60  |

| R28+07          | PIN2 | 166  | :50   | +5/GND | X:         | 5.80 | Y:-0.60  |

| R30+07 | PINS | 167 | : GND | +5/GND | X: 6.20 Y:-0.60 |

|--------|------|-----|-------|--------|-----------------|

| R3 27  | PINS | 168 | :50   | +5/GND | X: 6.50 Y:-0.60 |

| R33-07 | PINS | 169 | : GND | +5/GND | X: 6.90 Y:-0,60 |

| R34+07 | PINS | 170 | :50   | +5/GND | X: 7.20 Y:-0.60 |

| R36+07 | PINS | 171 | : GND | +5/GND | X: 7.60 Y:-0.60 |

| R38+07 | PINS | 172 | :50   | +5/GND | X: 8.00 Y:-0.60 |

| R40+07 | PINS | 173 | : GND | +5/GND | X: 8.40 Y:-0.60 |

| R42+07 | PINS | 174 | :5V   | +5/GND | X: 8.80 Y:-0.60 |

| R44+07 | PINS | 175 | : GND | +5/GND | X: 9.20 Y:-0.60 |

| R46+07 | PINS | 176 | :50   | +5/GND | X: 9.60 Y:-0.60 |

| R48+07 | PINS | 177 | : GND | +5/GND | X:10.00 Y:-0.60 |

| R5Ø+Ø7 | PINS | 178 | :5V   | +5/GND | X:10.40 Y:-0.60 |

| R52+07 |      | 179 | : GND | +5/GND | X:10.80 Y:-0.60 |

| R54+07 |      | 180 | :5∪   | +5/GND | X:11.20 Y:-0.60 |

| RØ1+19 |      | 181 | : GND | +5/GND | X: 0.10 Y:-1.80 |

| RØ3+19 |      | 182 | : 5V  | +5/GND | X: 0.50 Y:-1.80 |

| RØ5+19 | PINS | 183 | : GND | +5/GND | X: 0.90 Y:-1.80 |

| RØ7+19 |      | 184 | :50   | +5/GND | X: 1.30 Y:-1.80 |

| RØ9+19 |      | 185 | GND   | +5/GND | X: 1.70 Y:-1.80 |

| R11+19 |      | 186 | :50   | +5/GND | X: 2.10 Y:-1.80 |

| R13+19 |      | 187 | : GND | +5/GND | X: 2.50 Y:-1.80 |

| R15+19 |      | 188 | :50   | +5/GND | X: 2.90 Y:-1.80 |

| R17+19 |      | 189 | GND   | +5/GND | X: 3.30 Y:-1.80 |

| R19+19 |      | 190 | :50   | +5/GND | X: 3.70 Y:-1.80 |

| R21+19 |      | 191 | GND   | +5/GND | X: 4.10 Y:-1.80 |

| R22+19 |      | 192 | :50   | +5/GND | X: 4.40 Y:-1.80 |

| R24+19 |      | 193 | : GND | +5/GND | X: 4.80 Y:-1.80 |

| RZ 19  |      | 194 | :50   | +5/GND | X: 5.10 Y:-1.80 |

| R27+19 |      | 195 | GND   | +5/GND | X: 5.50 Y:-1.80 |

| R28+19 |      | 196 | :5V   | +5/GND | X: 5.80 Y:-1.80 |

| R3Ø+19 |      | 197 | GND   | +5/GND | X: 6.20 Y:-1.80 |

| R31+19 |      | 198 | :5V   | +5/GND | X: 6.50 Y:-1.80 |

| R33+19 |      | 199 | GND   | +5/GND | X: 6.90 Y:-1.80 |

| R34+19 |      | 200 | :54   | +5/GND | X: 7,20 Y:-1.80 |

| R36+19 |      | 201 | : GND | +5/GND | X: 7.60 Y:-1.80 |

| R38+19 |      | 202 | : 5V  | +5/GND | X: 8.00 Y:-1.80 |

| R40+19 |      | 203 | GND   | +5/GND | X: 8.40 Y:-1.80 |

| R42+19 |      | 204 | :50   | +5/GND | X: 8.80 Y:-1.80 |

| R44+19 |      | 205 | : GND | +5/GND | X: 9.20 Y:-1.80 |

| R46+19 |      | 206 | :5∨   | +5/GND | X: 9.60 Y:-1.80 |

| R48+19 |      | 207 | : GND | +5/GND | X:10,00 Y:-1.80 |

| R50+19 |      | 208 | :50   | +5/GND | X:10.40 Y:-1.80 |

| R52+19 |      | 209 | : GND | +5/GND | X:10.80 Y:-1.80 |

| R54+19 |      | 210 | :50   | +5/GND | X:11.20 Y:-1.80 |

| RØ1+31 |      | 211 | : GND | +5/GND | X: 0.10 Y:-3.00 |

| RØ3+31 |      | 212 | :50   | +5/GND | X: 0.50 Y:-3.00 |

| RØ5+31 |      | 213 | : GND | +5/GND | X: 0.90 Y:-3.00 |

| RØ7+31 |      | 214 | :50   | +5/GND | X: 1.30 Y:-3.00 |

| RØ9+31 |      | 215 | : GND | +5/GND | X: 1.70 Y:-3.00 |

| R11+31 |      | 216 | :50   | +5/GND | X: 2.10 Y:-9.00 |

| R13+31 |      | 217 | : GND | +5/GND | X: 2.50 Y:-3.00 |

| R15+31 |      | 216 | : 5V  | +5/GND | X: 2.90 Y:-3.00 |

| R1 31  |      | 219 | : GND | +5/GND | X: 3.30 Y:-3.00 |

| RI 31  |      | 220 | :50   | +5/GND | X: 3.70 Y:-3.00 |

| R21+31 |      | 221 | : GND | +5/GND | X: 4.10 Y:-3.00 |

| R22+31 |      | 222 | :50   | +5/GND | X: 4.40 Y:-3.00 |

|        |      |     | = *   |        | 11.12 1.4 2.00  |

| R24+31 | PINS                    | 223 | : GND | +5/GND | X: 4.80 Y:-3.00 |

|--------|-------------------------|-----|-------|--------|-----------------|

| R2-131 | PINS                    | 224 | :5∪   | +5/GND | X: 5.10 Y:-3.00 |

| R2 +31 | PINS                    | 225 | : GND | +5/GND | X: 5.50 Y:-9.00 |

| R28+31 | PINS                    | 226 | :50   | +5/GND | X: 5,80 Y:~9.00 |

| R30+31 | PINS                    | 227 | : GND | +5/GND | X: 6.20 Y:-3.00 |

| R31+31 |                         | 228 | :50   | +5/GND | X: 6.50 Y:-3.00 |

| R33+31 |                         | 229 | : GND | +5/GND | X: 6.90 Y:~3.00 |

| R34+31 |                         | 230 | :50   | +5/GND | X: 7.20 Y:-3.00 |

| R36+31 |                         | 231 | : GND | +5/GND | X: 7.60 Y:-3.00 |

| R38+31 | 70 J. S. S. S. S. S. S. | 232 | :50   | +5/GND | X: 8.00 Y:-3.00 |

| R40+31 |                         | 233 | : GND | +5/GND | X: 8.40 Y:-3.00 |

| R42+31 |                         | 234 | :5V   | +5/GND | X: 8.80 Y:-3.00 |

| R44+31 |                         | 235 | GND   | +5/GND | X: 9.20 Y:-3.00 |

| R46+31 |                         | 236 | :50   | +5/GND | X: 9.60 Y:~3.00 |

| R48+31 |                         | 237 | : GND | +5/GND | X:10.00 Y:-3.00 |

| R50+31 |                         | 238 | :50   | +5/GND | X:10.40 Y:-3.00 |

| R52+31 |                         | 239 | GND   | +5/GND | X:10.80 Y:-3.00 |

| R54+31 |                         | 240 | :50   | +5/GND | X:11.20 Y:-3.00 |

| RØ1+43 | 111                     | 241 | : GND | +5/GND | X: 0.10 Y:-4.20 |

| R03+43 |                         | 242 | :54   | +5/GND | X: 0.50 Y:-4.20 |

| R05+43 |                         | 243 | GND   | +5/GND | X: 0.90 Y:-4.20 |

| R07+43 |                         | 244 | :54   | +5/GND | X: 1.30 Y:-4.28 |

| RØ9+43 |                         | 245 | GND   | +5/GND | X; 1.78 Y;-4.28 |

| R11+43 |                         | 246 | :54   | +5/GND | X: 2.10 Y:-4.20 |

| R13+43 |                         | 247 | : GND | +5/GND | X: 2.50 Y:-4.20 |

| R15+43 |                         | 248 | :50   | +5/GND | X: 2.90 Y:-4.20 |

| R17+43 |                         | 249 | : GND | +5/GND | X: 3,30 Y:-4.20 |

| R1 43  |                         | 250 | :50   | +5/GND | X: 3.70 Y:~4.20 |

| R21+43 |                         | 251 | : GND | +5/GND | X: 4,10 Y:-4,28 |

| R22+43 |                         | 252 | :50   | +5/GND | X: 4.40 Y:-4.20 |

| R24+43 |                         | 253 | GND   | +5/GND | X: 4.80 Y:-4.20 |

| R25+43 |                         | 254 | :50   | +5/GND | X: 5.10 Y:-4.20 |

| R27+43 |                         | 255 | GND   | +5/GND | X: 5.50 Y:-4.20 |

| R28+43 |                         | 256 | :50   | +5/GND | X: 5.80 Y:-4.20 |

| R3Ø+43 |                         | 257 | : GND | +5/GND | X: 6.20 Y:-4,20 |

| R31+43 |                         | 258 | :50   | +5/GND | X: 6.50 Y:-4.20 |

| R33+43 |                         | 259 | : GND | +5/GND | X: 6.90 Y:-4.20 |

| R34+43 | PINS                    |     | :50   | +5/GND | X: 7.20 Y:-4.20 |

| R36+43 |                         | 261 | : GND | +5/GND | X: 7.60 Y:-4.20 |

| R38+43 |                         | 262 | :50   | +5/GND | X: 8.00 Y:-4.20 |

| R40+43 |                         | 263 | : GND | +5/GND | X: 8.48 Y:-4.28 |

| R42+43 | PINS                    | 264 | :50   | +5/GND | X: 8.88 Y;-4.28 |

| R44+43 |                         | 265 | : GND | +5/GND | X: 9.20 Y:-4.20 |

| R46+43 |                         | 266 | :50   | +5/GND | X: 9.60 Y:-4.28 |

| R48+43 |                         | 267 | : GND | +5/GND | X:10.00 Y:-4.20 |

| R50+43 |                         | 268 | :50   | +5/GND | X:10.40 Y:-4.20 |

| R52+43 |                         | 269 | : GND | +5/GND | X:10.80 Y:-4.20 |

| R54+43 |                         | 270 | :50   | +5/GND | X:11.20 Y:-4.20 |

| RØ3+55 |                         | 271 | :50   | +5/GND | X: 0.50 Y:-5.40 |

| RØ5+55 |                         | 272 | : GND | +5/GND | X: 0.90 Y:-5.40 |

| R07+55 |                         | 273 | :50   | +5/GND | X: 1.30 Y:-5.40 |

| RØ9+55 |                         | 274 | : GND | +5/GND | X: 1.78 Y:-5.48 |

| R11+55 |                         | 275 | :50   | +5/GND | X: 2.10 Y:-5.48 |

| R1 55  |                         | 276 | : GND | +5/GND | X: 2.50 Y:-5.40 |

| R15+55 |                         | 277 | :5U   | +5/GND | X: 2.90 Y:-5.40 |

| R17+55 |                         | 278 | GND   | +5/GND | X: 3.30 Y:-5.48 |

|        | -7. X-W-92              |     |       |        |                 |

| R19+55        | PINS    | 279 | :5∪    | +5/GND               | X: 3.70 Y:-5.40                         |

|---------------|---------|-----|--------|----------------------|-----------------------------------------|

| R2 <b>5</b> 5 | PINS    | 280 | : GND  | +5/GND               | X: 4.10 Y:-5.40                         |

| R22-55        | PINS    | 281 | :50    | +5/GND               | X: 4.40 Y:-5.40                         |