)

Created by WebCo Problems? Contact CCHD: by email or at 845-CCHD (2243).

For Review and Approval process questions please contact the Application Process Owner

### **Tutorial M06**

David E. Keyes

SC2006 Tutorial DeBenedictis, Keyes, Kogge

#### http://www.siam.org/news/ ("current issue")

### Taking on the ITER Challenge, Scientists Look to Innovative Algorithms, Petascale Computers

#### By Michelle Sipics

The promise of fusion as a clean, self-sustaining and essentially limitless energy source has become a mantra for the age, held out by many scientists as a possible solution to the world's energy crisis and a way to reduce the amounts of greenhouse gases released into the atmosphere by more conventional sources of energy. If self-sustaining fusion reactions can be realized and maintained long enough to produce electricity, the technology could potentially revolutionize energy generation and use.

ITER, initially short for International Thermonuclear Experimental Reactor, is now the official, non-acronymic name (meaning "the way" in Latin) of what is undoubtedly the largest undertaking of its kind. Started as a collaboration between four major parties in 1985, ITER has evolved into a seven-party project that finally found a physical home last year, when it was announced that the ITER fusion reactor would be built in Cadarache, in southern France. (The participants are the European Union, Russia, Japan, China, India, South Korea, and the United States.) In May, the seven initialed an agreement documenting the negotiated terms for the construction, operation, and decommissioning of the ITER tokamak, signifying another milestone for both the project itself and its eventual goal of using fusion to facilitate large-scale energy generation for the world.

Problems remain, however—notably the years, and perhaps decades of progress needed to attain such a goal. In fact, even simulating the proposed ITER tokamak is currently out of reach. But according to David Keyes, a computational mathematician at Columbia University and acting director of the Institute for Scientific Computing Research (ISCR) at Lawrence Livermore National Laboratory, the ability to perform such simulations may be drawing closer.

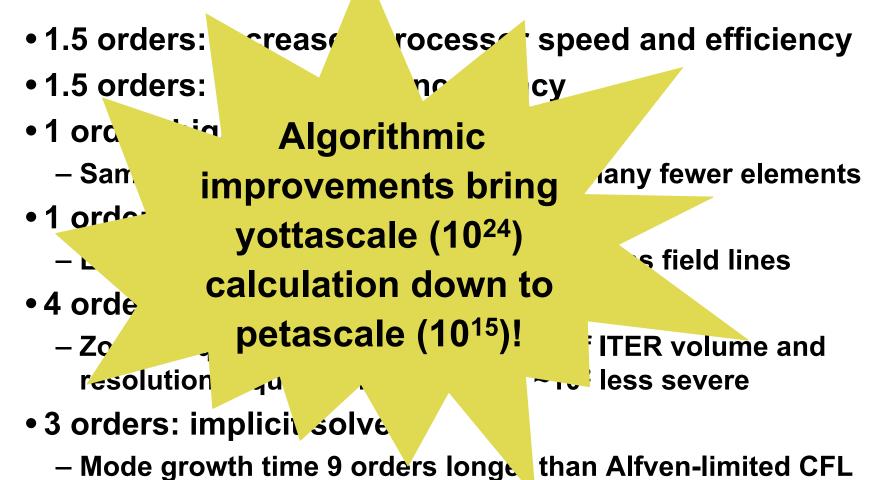

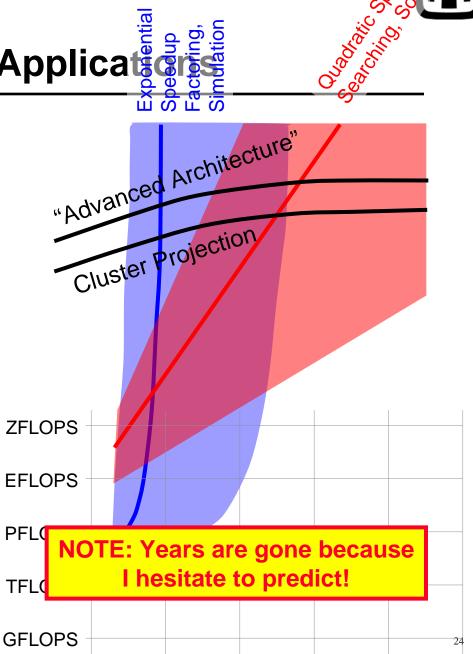

#### Hardware 3, Software 9

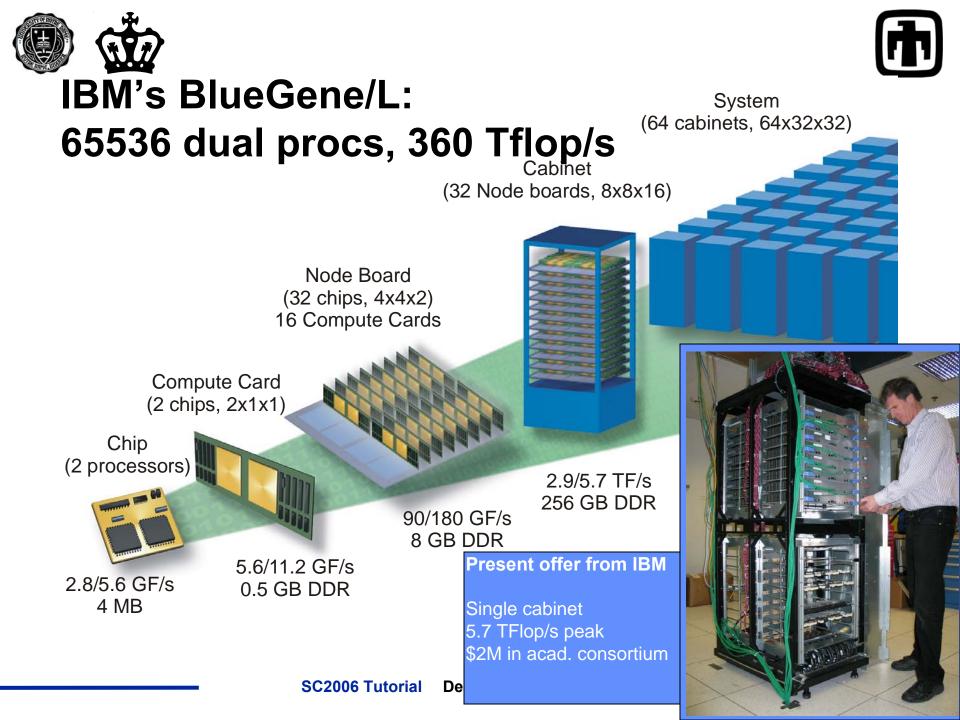

"Fusion scientists have been making useful characterizations about plasma fusion devices, physics, operating regimes and the like for over 50 years," Keyes says. "However, to simulate the dynamics of ITER for a typical experimental 'shot' over scales of interest with today's most commonly used algorithmic technologies would require approximately 10<sup>24</sup> floating-point operations." That sounds bleak, given the 280.6 Tflop/s (10<sup>12</sup> flops/s) benchmark performance of the IBM BlueGene/L at Lawrence Livermore National Laboratory—as of June the fastest supercomputer in the world. But Keyes is optimistic: "We expect that with proper algorithmic ingenuity, we can reduce this to 10<sup>15</sup> flops."

Optimizing the algorithms used, in other words, could lower the computing power required for some ITER simulations by an astounding nine orders of magnitude. Even more exciting, those newly feasible simulations would be at the petascale—ready to run on the petaflop/s supercomputers widely expected within a few years.

The ingenuity envisioned by Keyes even has a roadmap. Together with Stephen Jardin of the Princeton Plasma Physics Laboratory. Dyes developed a breakdown that explains where as many as 12 orders of magnitude of speedup will come from over the next decade: 1.5 from increased parallelism, 1.5 from greater processor speed and efficiency, four from adaptive gridding, one from higher-order elements, one from field-line following coordinates, and three from implicit algorithms.

#### SC2006 Tutorial DeBenedictis, Keyes, Kogge

### **Presentation Features**

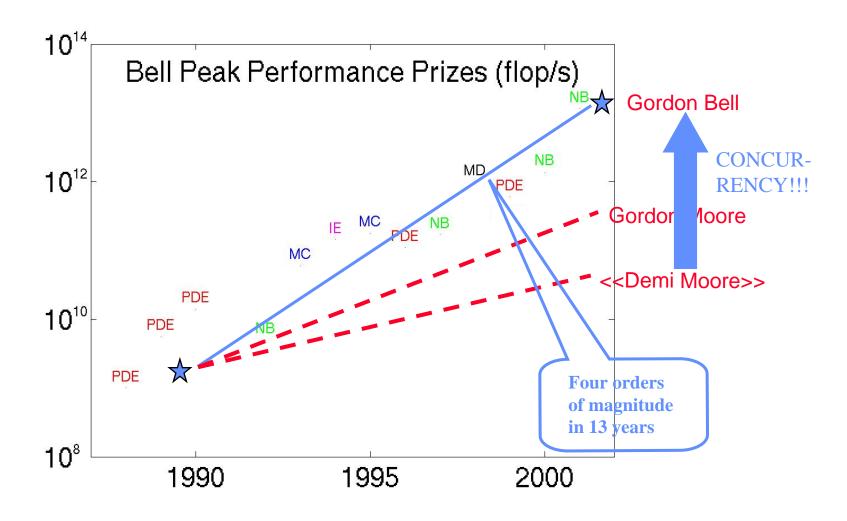

- Briefly reflect on recent progress in high-end scientific computing, as illustrated on Bell Prize-winning applications – why?

- Bell has attracted high-end attention thru two decades of architectures

- Winners document performance issues beyond details found in other computational science papers, which instead emphasize science

- PDE-based simulations are the dominant type of Bell submission

- Performance-orientation exposes an interesting fallacy for our discussion <sup>©</sup>

- Look generically at PDE-based simulation and the basis of continued optimism for its growth – capability-wise, looking at real applications

- Look at some specific hurdles to PDE-based simulation posed by highend architecture

- Study in detail an unstructured Bell Prize entry to note architectural stresses

### **Technical aspects of presentation**

- Introduce a parameterized highly tunable class of algorithms for parallel implicit solution of PDEs

- understand the source of their "weak scalability"

- understand their lack of "strong scalability"

- understand why explicit algorithms generally do not scale, even weakly, in the high spatial resolution limit

- Note some algorithmic "adaptations" to architectural stresses

### Gordon Bell Prize "peak performance"

| Year | Туре | Application    | No. Procs | System       | Gflop/s |              |

|------|------|----------------|-----------|--------------|---------|--------------|

| 1988 | PDE  | Structures     | 8         | Cray Y-MP    | 1.0     |              |

| 1989 | PDE  | Seismic        | 2,048     | CM-2         | 5.6     |              |

| 1990 | PDE  | Seismic        | 2,048     | CM-2         | 14      |              |

| 1992 | NB   | Gravitation    | 512       | Delta        | 5.4     |              |

| 1993 | MC   | Boltzmann      | 1,024     | CM-5         | 60      |              |

| 1994 | IE   | Structures     | 1,904     | Paragon      | 143     |              |

| 1995 | MC   | QCD            | 128       | NWT          | 179     | Five orders  |

| 1996 | PDE  | CFD            | 160       | NWT          | 111     | rive orders  |

| 1997 | NB   | Gravitation    | 4,096     | ASCI Red     | 170     | of magnitude |

| 1998 | MD   | Magnetism      | 1,536     | T3E-1200     | 1,020   | in 17 years  |

| 1999 | PDE  | CFD            | 5,832     | ASCI BluePac | 627     | m 17 years   |

| 2000 | NB   | Gravitation    | 96        | GRAPE-6      | 1,349   |              |

| 2001 | NB   | Gravitation    | 1,024     | GRAPE-6      | 11,550  |              |

| 2002 | PDE  | Climate        | 5,120     | Earth Sim    | 26,500  |              |

| 2003 | PDE  | Seismic        | 1,944     | Earth Sim    | 5,000   |              |

| 2004 | PDE  | CFD            | 4,096     | Earth Sim    | 15,200  |              |

| 2005 | MD   | Solidification | 131,072   | BG/L         | 101,700 |              |

### Gordon Bell Prize outpaces Moore's Law

### Tally of Peak Prize formulations and apps

- $\bullet$  8  $\times$  Partial differential equations

- Climate, fluids, seismology, structures

- 4  $\times$  N-body dynamics

- Gravitation

- $\bullet$  3  $\times$  Molecular dynamics

- Electronic structure, magnetism, solidification

- 2  $\times$  Monte Carlo methods

- Boltzmann, Quantum Chromodynamics

- •1 × Integral equations

- Structures

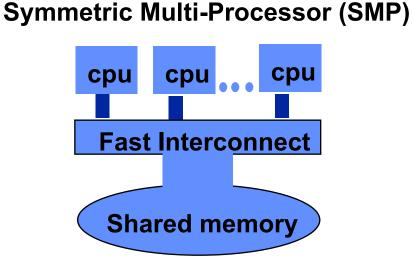

### **Tally of Gordon Bell Peak Prize hardware**

- two to hundreds of processors

- shared memory

- global addressing

- 4 prizes, last in 1993

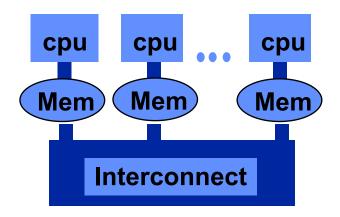

**Massively Parallel Processor (MPP)**

- thousands to hundreds of thousands of processors

- distributed memory

- local addressing

- 13 prizes, including last 12

### The "other" Bell prizes

- "Peak" is only one of several types of Gordon Bell Prizes that have been awarded over the years

- The only one awarded each time there have been Bell Prizes

- "Price-performance" has been recognized 12 times, but not since 2001, when it stagnated at about 25 cents per delivered Mflop/s

- A few of these have been for implementations of PDEs

- "Special" was first awarded in 1999 and has sometimes inspired multiple awards per year

- *Most* of these have gone to implementation of PDEs

- "Compiler-derived parallelism" has been awarded three times, most recently in 2002 for HPF

- Two of these have gone to implementations of PDEs

- "Speedup" (strong, that is) was explicitly recognized once, in 1992

- For an implementation of a PDE

### Gordon Bell Prize: "price performance"

| Year | Application          | System      | \$ per Mflops         |

|------|----------------------|-------------|-----------------------|

| 1989 | Reservoir modeling   | <b>CM-2</b> | 2,500                 |

| 1990 | Electronic structure | IPSC        | 1,250                 |

| 1992 | Polymer dynamics     | cluster     | 1,000                 |

| 1993 | Image analysis       | custom      | 154                   |

| 1994 | Quant molecular dyn  | cluster     | 333                   |

| 1995 | Comp fluid dynamics  | cluster     | 278 Four order        |

| 1996 | Electronic structure | SGI         | 159 <b>of magnitu</b> |

| 1997 | Gravitation          | cluster     | 56 in 12 years        |

| 1998 | Quant chromodynamics | custom      | 12.5                  |

| 1999 | Gravitation          | custom      | 6.9                   |

| 2000 | Comp fluid dynamics  | cluster     | 1.9                   |

| 2001 | Structural analysis  | cluster     | 0.24                  |

### Whimsical remarks on Bell, 1988-2005

- If similar improvements in speed (10<sup>5</sup>) had been realized in the airline industry, a 3-hour flight would require one-tenth of a second today

- If similar reductions in cost (10<sup>4</sup>) had been realized in higher education, tuition room and board would cost about \$2 per year

- If similar improvements in storage (10<sup>4</sup>) had been realized in the publishing industry, our office bookcases could hold the book portion of the collection of the Library of Congress (~18M volumes)

Gedanken experiment: How to use a jar of peanut butter with a rapidly dropping price?

- In 2006, at \$3.19: make sandwiches

- By 2009, at \$0.80: make recipe substitutions

- By 2012, at \$0.20: use as feedstock for biopolymers, plastics, etc.

- . By 2115, at \$0.05: heat homes

- . By 2118, at \$0.012: pave roads 🙂

The cost of computing has been on a curve like this for two decades. Can we count on another decade? If so, like everyone else, scientists & engineers should plan increasing uses for it. If *not* ...

### Performance vs. time-to-solution

- Gordon Bell peak prizes cannot, by definition, go to threadnonuniform, flop-bare simulations

- Prizes tend to concentrate in regular, Cartesian index space, flop-rich computations

- There is a conflict between what the peak prize measures and

- what is good for the computational science community, in terms of getting its work done

- what is good for the computational mathematics community, in terms of identifying interesting problems

- The "special" prize attempts to remedy this shortcoming of the traditional prize, and is often the most interesting category

### Gordon Bell Prize: "special"

| Year | Application           | Discretization | System          |

|------|-----------------------|----------------|-----------------|

| 1999 | Aerodynamics          | unstructured   | Intel ASCI Red  |

| 1999 | Stellar physics       | spectral       | Intel ASCI Red  |

| 2000 | Reactive flow         | Cartesian AMR  | Intel ASCI Red  |

| 2001 | Relativistic fields   | structured     | cluster         |

| 2002 | Structural dynamics   | unstructured   | IBM ASCI White  |

| 2002 | DNS                   | structured     | Earth Simulator |

| 2002 | Biomolecular dynamics |                |                 |

| 2003 | Seismic inversion     | unstructured   | HP LeMieux      |

| 2004 | Bone mechanics        | unstructured   | IBM ASCI White  |

8 of 9 "special" awards have gone to PDE simulations

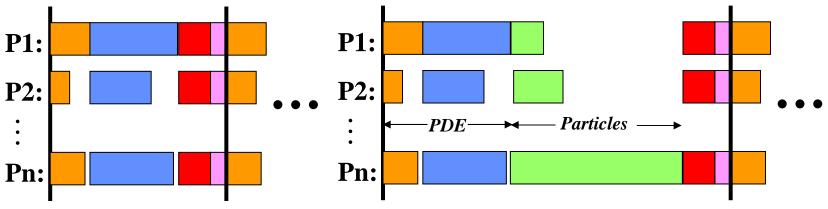

### 1999 Gordon Bell "special" prize

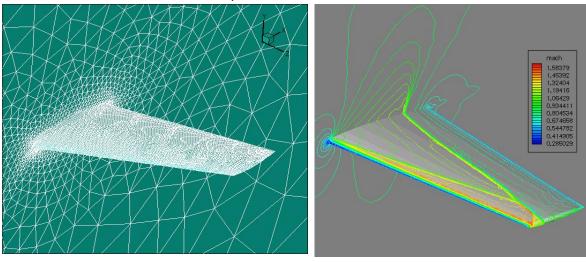

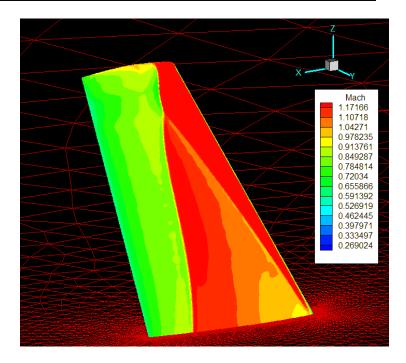

- 1999 Bell Prize in "special category" went to implicit, unstructured grid aerodynamics problems

- 0.23 Tflop/s sustained on 3 thousand processors of Intel's ASCI Red

- 11 million degrees of freedom

- incompressible and compressible Euler flow

- employed in NASA analysis/design missions

Transonic "Lambda" Shock, Mach contours on surfaces

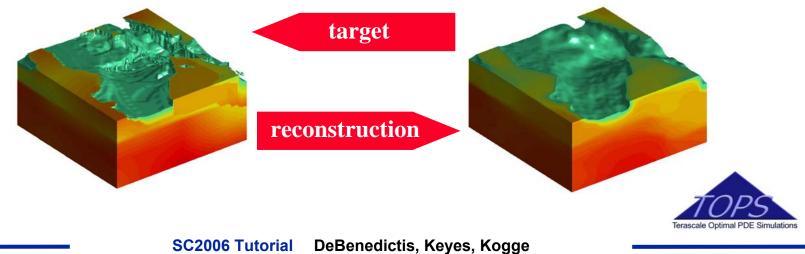

### 2003 Gordon Bell "special" prize

- 2003 Bell Prize in "special category" went to unstructured grid geological parameter estimation problem

- 1 Tflop/s sustained on 2 thousand processors of HP's "Lemieux

- each explicit forward PDE solve: 17 million degrees of freedom

- seismic inverse problem: 70 billion degrees of freedom

- employed in NSF seismic research at CMU

c/o O. Ghattas, UT Austin

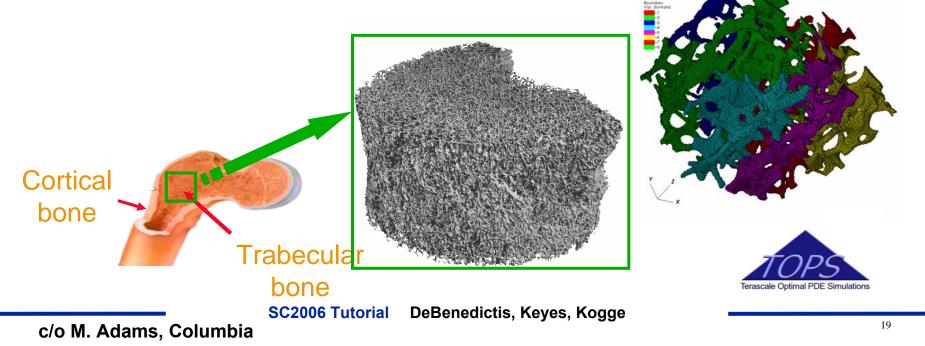

### 2004 Gordon Bell "special" prize

- 2004 Bell Prize in "special category" went to an implicit, unstructured grid bone mechanics simulation

- 0.5 Tflop/s sustained on 4 thousand procs of IBM's ASCI White

- 0.5 billion degrees of freedom

- large-deformation analysis

- employed in NIH bone research at Berkeley

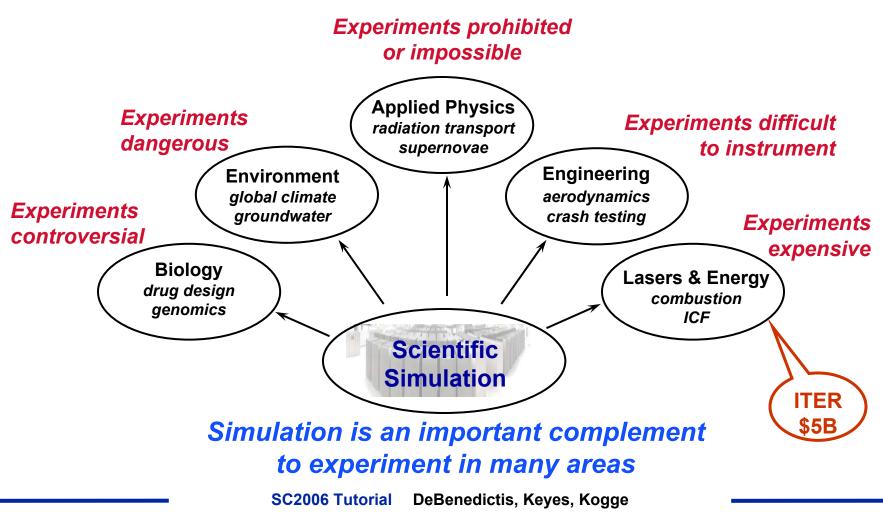

## Terascale simulation is pitched as an alternative to (some) experimentation

# Context: many recent reports promote high-end simulation

- Cyberinfrastructure (NSF, 2003)

- new research environments through cyberinfrastructure

- Facilities for the Future of Science (DOE, 2003)

- "ultrascale simulation facility" ranked #2 behind ITER only

- High End Computing Revitalization Task Force (Interagency, 2004)

- strategic planning on platforms

- Future of Supercomputing (NAS, 2005)

- broad discussion of the future of supercomputing

- PITAC (Interagency, 2005)

- challenges in software and in interdisciplinary training

- Simulation-based Engineering Science (NSF, 2006)

- opportunities in dynamic, data-driven simulation and engineering design

- Advanced Nuclear Energy Simulations (DOE, 2006)

- SCaLeS report, Vol 1 (DOE, 2003) & Vol 2 (DOE, 2004)

- implications of large-scale simulation for basic scientific research

- Capability Computing Needs (DOE, 2004)

- profiles of leading edge DOE codes in 11 application domains

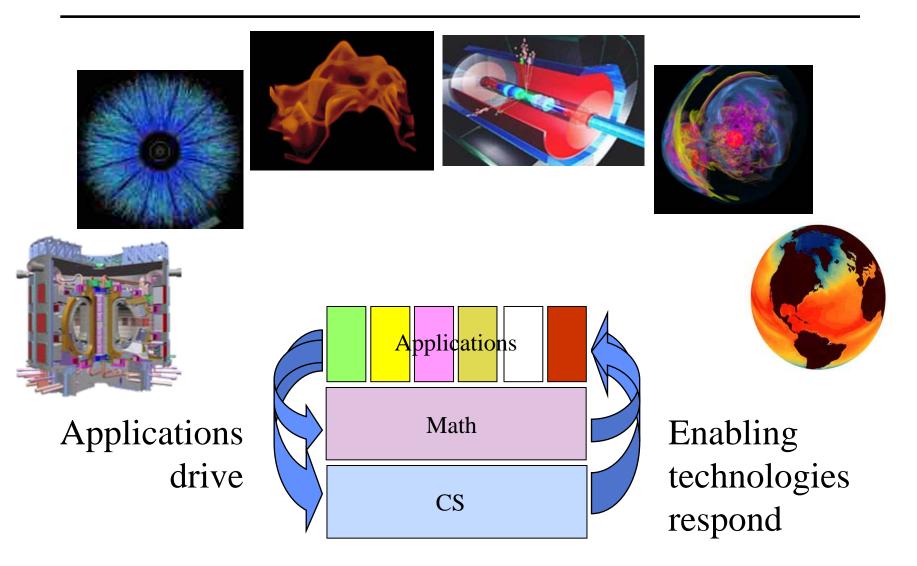

## **Diverse applications, common algorithmic and architectural infrastructure**

### A primary source: SCaLeS

- Chapter 1. Introduction

- Chapter 2. Scientific Discovery through Advanced Computing: a Successful Pilot Program

- Chapter 3. Anatomy of a Large-scale Simulation

- Chapter 4. Opportunities at the Scientific Horizon

- Chapter 5. Enabling Mathematics and Computer Science Tools

- Chapter 6. *Recommendations and Discussion* Volume 2 (2004):

- 11 chapters on applications

- 8 chapters on mathematical methods

- 8 chapters on computer science and infrastructure

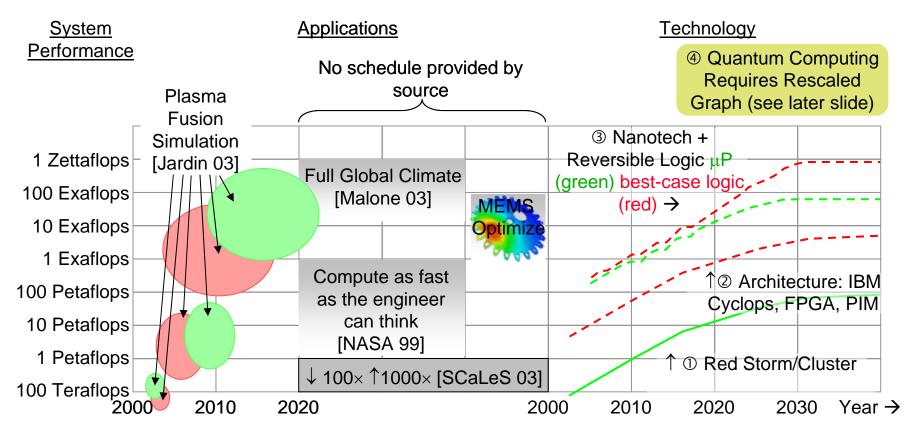

# "What would scientists do with 100-1000x?" (SCaLeS)

- Predict future climates

- Probe structure of particles

- Design accelerators

- Design and control tokamaks

- Control combustion

- Probe supernovae

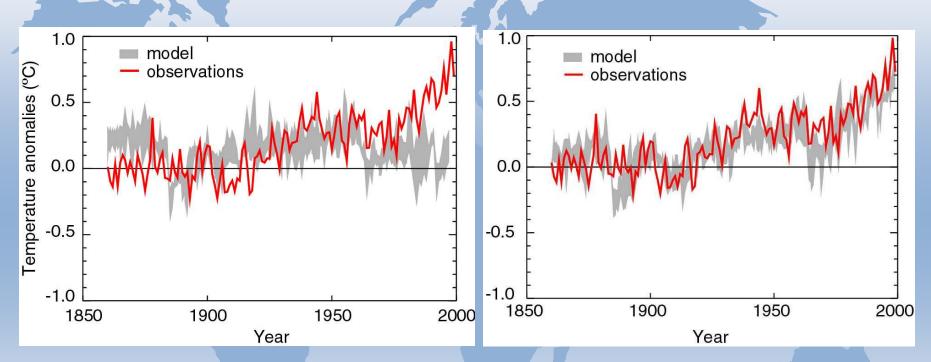

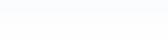

## What would scientists do with 100-1000x? **Example: predict future climates**

- Resolution

- refine horizontal in atmosphere from 160 to 40 km

- refine horizontal in ocean from 105 to 15km

- New "physics"

- atmospheric chemistry

- carbon cycle

- dynamic terrestrial vegetation (nitrogen and sulfur cycles and land-use and land-cover changes)

- Improved representation of subgrid processes

- clouds

- atmospheric radiative transfer

### What would scientists do with 100-1000x? **Example: predict future climates**

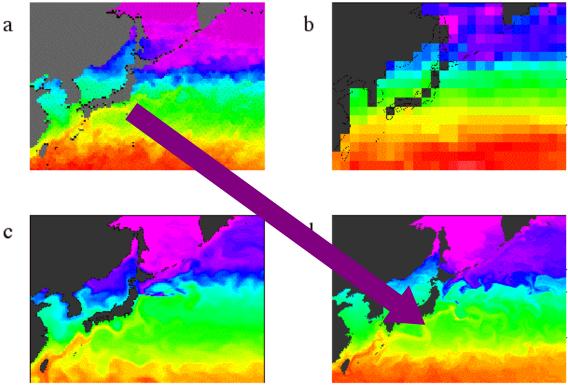

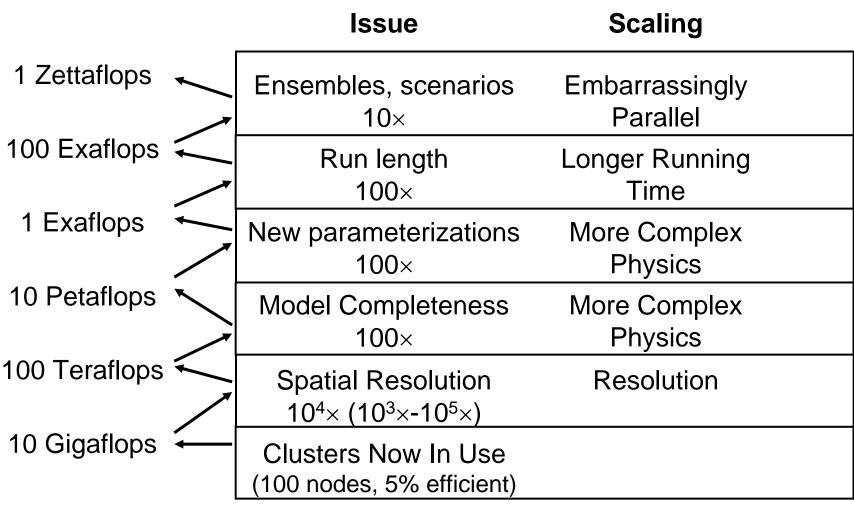

Resolution of Kuroshio Current: Simulations at various resolutions have demonstrated that, because equatorial meso-scale eddies have diameters ~10-200 km, the grid spacing must be < 10 km to adequately resolve the eddy spectrum. This is illustrated in four images of the sea-surface temperature. Figure (a) shows a snapshot from satellite observations, while the three other figures are snapshots from simulations at resolutions of (b)  $2^\circ$ , (c)  $0.28^\circ$ , and (d)  $0.1^\circ$ .

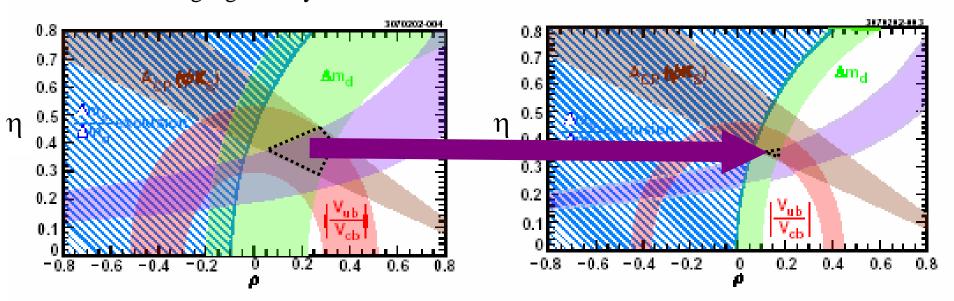

### Example: probe structure of particles

- Resolution

- take current 4D models from 32×32×32×16 to 128×128×128×64

- New physics

- "unquench" the lattice approximation: enable study of the gluon structure of the nucleon, in addition to its quark structure

- obtain chiral symmetry by solving on a 5D lattice in the domain wall Fermion formulation

- allow precision calculation of the spectroscopy of strongly interacting particles with unconventional quantum numbers, guiding experimental searches for states with novel quark and gluon structure

Constraints on the Standard Model parameters  $\rho$  and  $\eta$ . For the Standard Model to be correct, these parameters from the Cabibbo-Kobayashi-Maskawa (CKM) matrix must be restricted to the region of overlap of the solidly colored bands. The figure on the left shows the constraints as they exist today. The figure on the right shows the constraints as they would exist with no improvement in the experimental errors, but with lattice gauge theory uncertainties reduced to 3%.

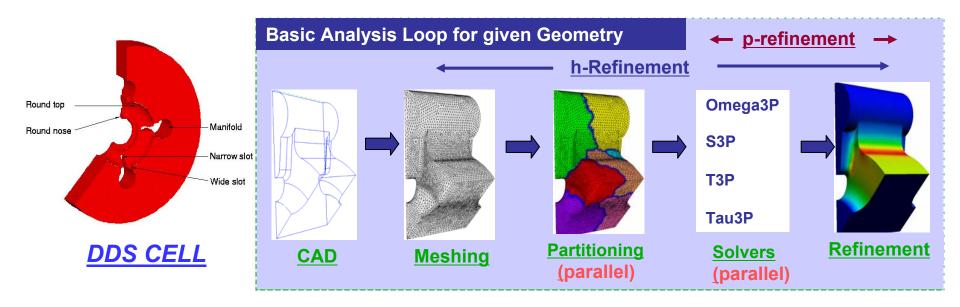

### Resolution

- complex geometry (long assemblies of damped detuned structure (DDS) cells, each one slightly different than its axial neighbor) requires unstructured meshes with hundreds of millions of degrees of freedom

- Maxwell eigensystems for interior elements of the spectrum must be solved in the complex cavity formed by the union of the DDS cells

- Novel capability

- PDE-based mathematical optimization will replace expensive and slow trial and error prototyping approach

- each inner loop of optimization requires numerous eigensystem analyses

## What would scientists do with 100-1000x? **Example: design accelerators**

*Next generation accelerators have complex cavities.* Shape optimization is required to improve performance and reduce operating cost.

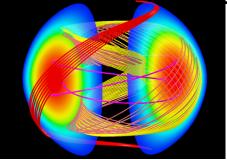

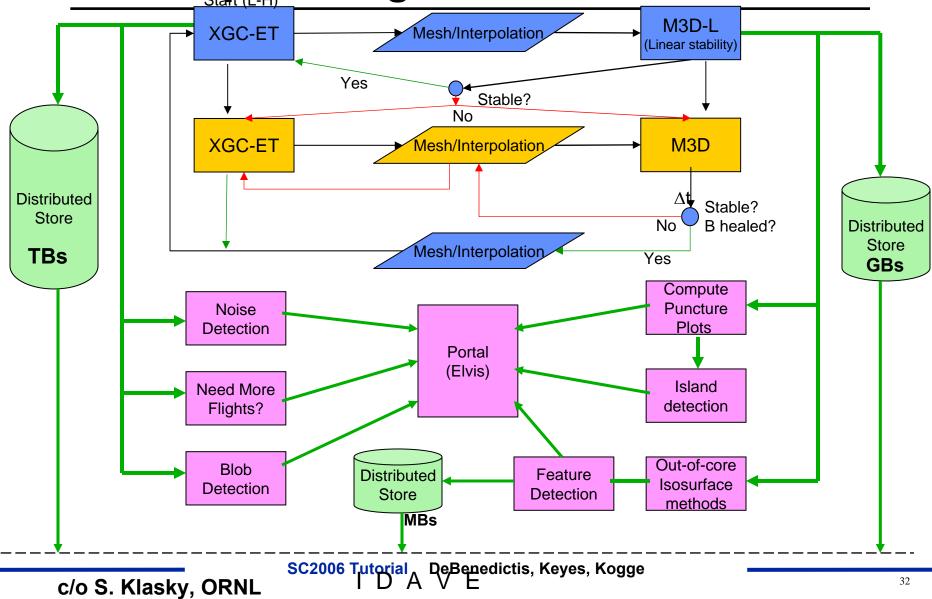

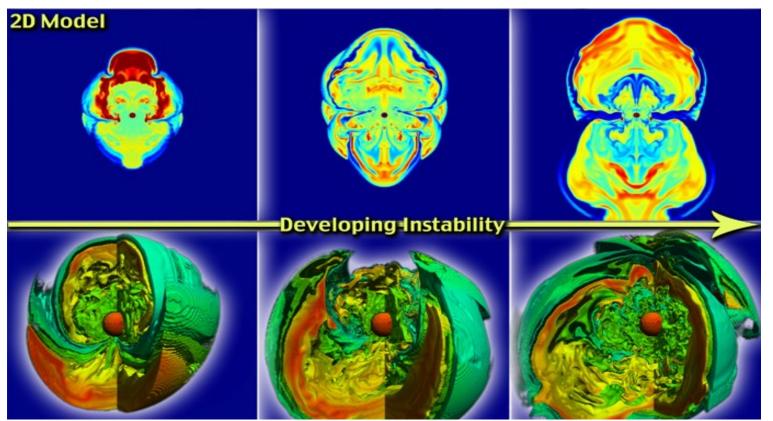

### Example: design and control tokamaks

- Resolution

- refine meshes and approach physical Lundquist numbers

- Multiphysics

- combine MHD, PIC, and RF codes in a single, consistent simulation

- resolve plasma edge

- Design and control

- optimize performance of experimental reactor ITER and follow-on production devices

- detect onset of instabilities and modify before catastrophic energy releases from the magnetic field

### What would scientists do with 100-1000x?

Example: design and control tokamaks

### Resolution

- evolve 3D time-dependent large-eddy simulation (LES) codes to direct Navier-Stokes (DNS)

- multi-billions of mesh zones required

- New "physics"

- explore coupling between chemistry and acoustics (currently filtered out)

- explore sooting mechanisms to capture radiation effects

- capture autoignition with realistic fuels

- Integrate with experiments

- pioneer simulation-controlled experiments to look for predicted effects in the laboratory

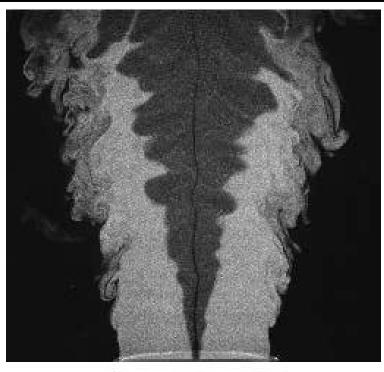

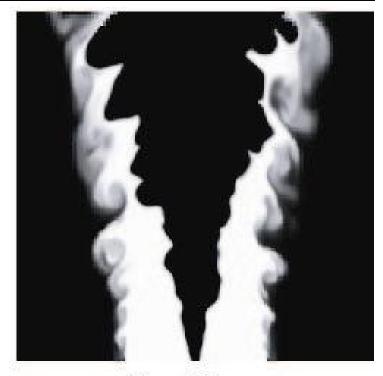

## What would scientists do with 100-1000x? **Example: control combustion**

#### Experimental PIV measurement

Instantaneous flame front imaged by density of inert marker

Simulation Instantaneous flame front imaged by fuel concentration

### Images c/o R. Cheng (left), J. Bell (right), LBNL, and NERSC 2003 SIAM/ACM Prize in CS&E (J. Bell & P. Colella)

SC2006 Tutorial DeBenedictis, Keyes, Kogge

### Example: probe supernovae

- Resolution

- current Boltzmann neutrino transport models are vastly under-resolved

- need at least 512<sup>3</sup> spatially, at least 8 polar and 8 azimuthal, and at least 24 energy groups energy groups per each of six neutrino types

- to discriminate between competing mechanisms, must conserve energy to within 0.1% over millions of time steps

- Full dimensionality

- current models capable of multigroup neutrino radiation are lower-dimensional; full 3D models are required

## What would scientists do with 100-1000x? **Example: probe supernovae**

*Stationary accretion shock instability defines shape of supernovae and direction of emitted radiation.* Lower dimensional models produce insight; full dimensional models are ultimately capable of providing radiation signatures that can be compared with observations.

SC2006 Tutorial DeBenedictis, Keyes, Kogge c/o A. Mezzacappa, ORNL

# **Progress in scaling PDE applications**

- Both structured and unstructured grids

- Both explicit and implicit methods

- Multiple decades of spatial "resolution"

- Many-thousand-fold concurrency

- Strong scaling within modest ranges

- Weak scaling (also called "scaled speedup") without obvious limits

# **Review: two definitions of scalability**

- "Strong scaling"

- execution time decreases in inverse proportion to the number of processors

- fixed size problem overall

- often instead graphed as reciprocal, "speedup"

- "Weak scaling"

- execution time remains constant, as problem size and processor number are increased in proportion

- fixed size problem per processor

- also known as "Gustafson scaling"

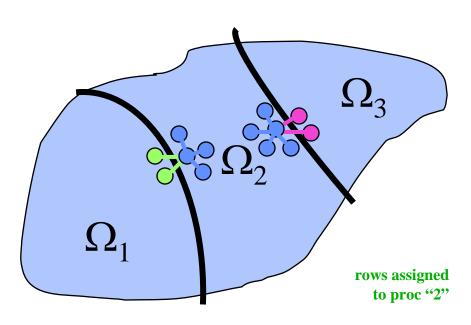

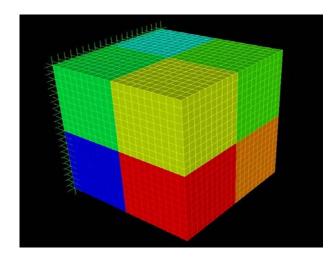

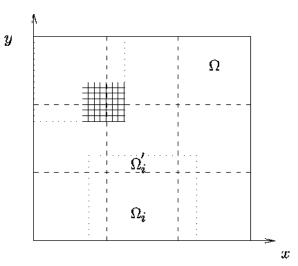

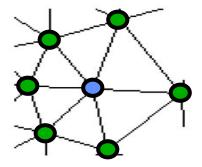

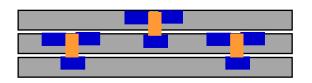

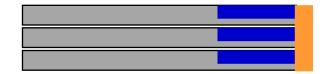

#### SPMD parallelism w/domain decomposition

(volume) work to (surface) communication is preserved under weak scaling

Partitioning of the grid induces block structure on the system matrix (Jacobian)

DD relevant to any local stencil formulation

5 Tutorial DeBenedictis, Keves, Kogg

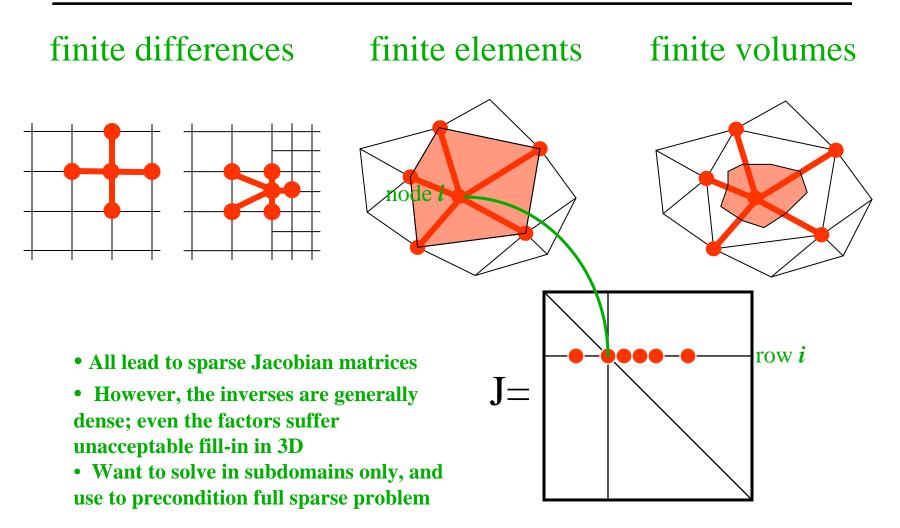

# An algorithm for PDE simulation: Newton-Krylov-Schwarz

sparse MATVECs,

inner products,

nonlinear residual

evaluations, inner

Krylov

accelerator

spectrally adaptive

Schwarz preconditioner *parallelizable*

local solves,

small global

# Krylov-Schwarz parallelization is simple!

- Decomposition into concurrent tasks

- by domain

- Assignment of tasks to processes

- typically one subdomain per process

- Orchestration of communication between processes

- to perform sparse matvec near neighbor communication

- to perform subdomain solve nothing

- to build Krylov basis global inner products

- to construct best fit solution global sparse solve (redundantly)

- Mapping of processes to processors

- typically one process per processor

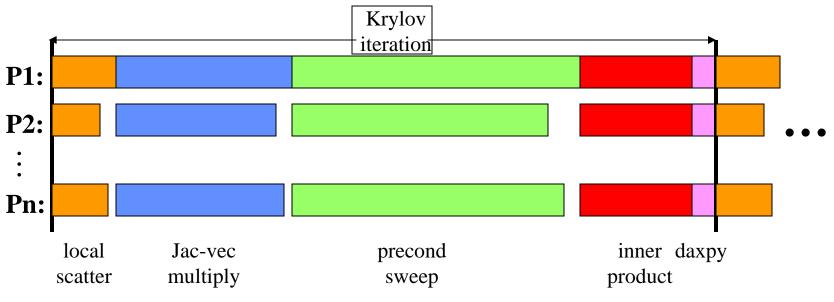

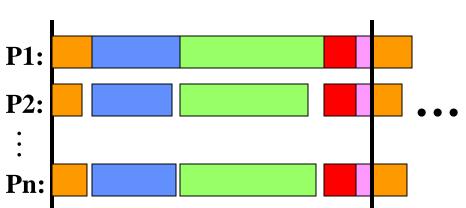

# Inner Krylov-Schwarz kernel: a Bulk Synchronous Process (BSP)

What happens if, for instance, in this (schematicized) iteration, arithmetic speed is *doubled*, scalar all-gather is *quartered*, and local scatter is *cut by one-third*? Each phase is considered separately. Answer is to the right.

- Given complexity estimates of the leading terms of:

- the concurrent computation (per iteration phase)

- the concurrent communication

- the synchronization frequency

- And a bulk synchronous model of the architecture including:

- internode communication (network topology and protocol reflecting horizontal memory structure)

- on-node computation (effective performance parameters including vertical memory structure)

- One can estimate optimal concurrency and optimal execution time

- on per-iteration basis, or overall (by taking into account any granularity-dependent convergence rate)

- simply differentiate time estimate in terms of (*N*,*P*) with respect to *P*, equate to zero and solve for *P* in terms of *N*

### Estimating 3D stencil costs (per iteration)

- grid points in each direction n, total work N=O(n<sup>3</sup>)

- processors in each direction

p, total procs P=O(p<sup>3</sup>)

- memory per node requirements O(N/P)

- concurrent execution time per iteration A n<sup>3</sup>/p<sup>3</sup>

- grid points on side of each processor subdomain n/p

- Concurrent neighbor commun. time per iteration *B n<sup>2</sup>/p<sup>2</sup>*

- cost of global reductions in each iteration C log p or C p<sup>(1/d)</sup>

- C includes synchronization frequency

- same dimensionless units for measuring A, B, C

- e.g., cost of scalar floating point multiply-add

Rich local network, tree-based global reductions

total wall-clock time per iteration

$$T(n,p) = A\frac{n^{3}}{p^{3}} + B\frac{n^{2}}{p^{2}} + C\log p$$

• for optimal *p*,  $\frac{\partial T}{\partial p} = 0$ , or  $3A\frac{n^{3}}{p^{4}} - 2B\frac{n^{2}}{p^{3}} + \frac{C}{p} = 0$ ,

or (with

$$\theta = \frac{32B^3}{243A^2C}$$

),

$p_{opt} = \left(\frac{3A}{2C}\right)^{\frac{1}{3}} \left(\left[1 + (1 - \sqrt{\theta})\right]^{\frac{1}{3}} + \left[1 - (1 - \sqrt{\theta})\right]^{\frac{1}{3}}\right) \cdot n$

• without "speeddown," p can grow with n

• in the limit as

$$\frac{B}{C} \rightarrow 0$$

$p_{opt} = \left(\frac{3A}{C}\right)^{\frac{1}{3}} \cdot n$

## Scalability results for DD stencil computations

- With tree-based (logarithmic) global reductions and scalable nearest neighbor hardware:

- optimal number of processors scales linearly with problem size

- With 3D torus-based global reductions and scalable nearest neighbor hardware:

- optimal number of processors scales as three-fourths power of problem size (almost "scalable")

- With common network bus (heavy contention):

- optimal number of processors scales as one-fourth power of problem size (not "scalable")

- This generic weak scaling type of argument has been made for ten years

- in Petaflops Workshop series (1995 onward)

- in "all-hands" group meetings of SciDAC users (2001 onward)

- Why aren't PDEs "humming" on BG/L?

- Of six announced finalists for Bell in 2006, only one is based on PDE simulation, and it achieves only 0.5 Tflop/s on 4K nodes of BG/L

- This compares with 200 Tflop/s on 64K nodes for MD on BG/L – a factor of 25 better in flop/s per node on 16 times more nodes for 400 × performance

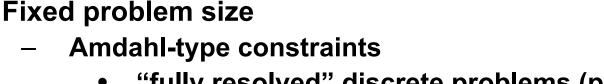

"fully resolved" discrete problems (protein folding, network problems)

**Contraindications of scalability**

- "sufficiently resolved" problems from the continuum

- Scalable problem size

- Resolution-limited progress in "long time" integration

- explicit schemes for time-dependent PDEs

- suboptimal iterative relaxations schemes for equilibrium PDEs

- Nonuniformity of threads

- adaptive schemes

- multiphase computations (e.g, particle and field)

- Fundamental limit to strong scaling due to small overheads

- Independent of number of processors available

- Analyze by binning code segments by degree of exploitable concurrency and dividing by available processors, up to limit

- Illustration for just two bins:

- fraction f<sub>1</sub> of work that is purely sequential

- fraction  $(1-f_1)$  of work that is arbitrarily concurrent

- Wall clock time for p processors

- Speedup  $\propto f_1 + (1 f_1) / p$  p 1 10 100 1000 10000 - for f\_1=0.01 S 1.0 9.2 50.3 91.0 99.0

- Applies to any performance enhancement, not just parallelism

$= 1/[f_1 + (1 - f_1)/p]$

**W**

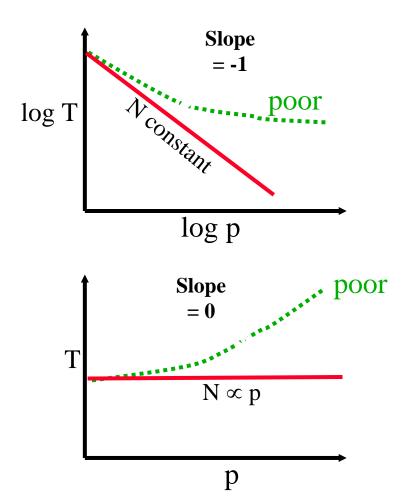

# **Resolution-limited progress (weak scaling)**

- Illustrate for CFL-limited

explicit time stepping

- Parallel wall clock time  $\propto T S^{1+lpha/d} P^{lpha/d}$

- Example: explicit wave problem in 3D (α=1, d=3)

| Domain    | 10 <sup>3</sup> × 10 <sup>3</sup> ×10 <sup>3</sup> | $10^{4} \times 10^{4} \times 10^{4}$ | 10 <sup>5</sup> × 10 <sup>5</sup> ×10 <sup>5</sup> |

|-----------|----------------------------------------------------|--------------------------------------|----------------------------------------------------|

| Exe. time | 1 day                                              | 10 days                              | 3 months                                           |

• Example: explicit diffusion problem in 2D

(α=2, d=2)

| Domain    | 10 <sup>3</sup> × 10 <sup>3</sup> | 10 <sup>4</sup> × 10 <sup>4</sup> | 10 <sup>5</sup> × 10 <sup>5</sup> |

|-----------|-----------------------------------|-----------------------------------|-----------------------------------|

| Exe. time | 1 day                             | 3 months                          | 27 years                          |

d-dimensional domain, length scale L d+1-dimensional space-time, time scale T h mesh cell size  $\tau$  time step size  $\tau = O(h^{\alpha})$  bound on time step *n=L/h* number of mesh cells in each dim *N=n<sup>d</sup>* number of mesh cells overall  $M=T/\tau$  number of time steps overall O(N) total work to perform one time step O(MN) total work to solve problem **P** number of processors S storage per processor *PS* total storage on all processors (=*N*) O(MN/P) parallel wall clock time  $\propto$  (T/ $\tau$ )(PS)/P  $\propto$  T S<sup>1+ $\alpha$ /d</sup> P<sup> $\alpha$ /d</sup> (since  $\tau \propto h^{\alpha} \propto 1/n^{\alpha} = 1/N^{\alpha/d} = 1/(PS)^{\alpha/d}$ )

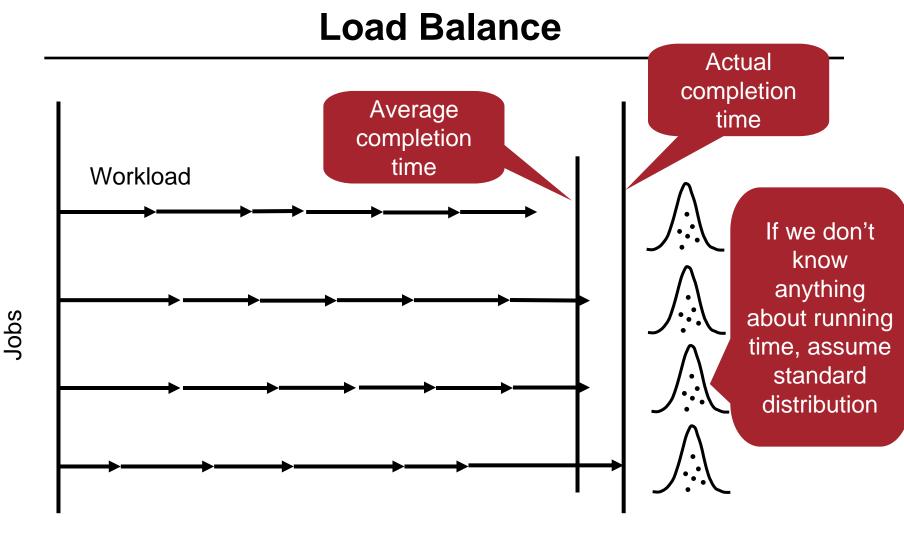

# **Thread nonuniformity**

- Evolving state of the simulation can spoil load balance

- adaptive scheme

- local mesh refinement

- local time adaptivity

- state-dependent work complexity

- complex constitutive or reaction terms

- nonlinear inner loops with variable convergence rates

- multiphase simulation

- bulk synchronous alternation between different phases with different work distributions

### **Algorithmic adaptation**

- No computer system is well balanced for all computational tasks, or even for all phases of a single well-defined task, like solving nonlinear systems arising from discretized differential equations

- Given the need for high performance in the solution of these and related systems, one should be aware of which computational phases are limited by which aspect of hardware or software.

- With this knowledge, one can design algorithms to "play to" the strengths of a machine of given architecture, or one can intelligently select or evolve architectures for preferred algorithms.

Four potential limiters on scalability in large-scale parallel scientific codes

- Insufficient localized concurrency

- Load imbalance at synchronization points

- Interprocessor message latency

- Interprocessor message bandwidth

"horizontal aspects"

# Four potential limiters on arithmetic performance

- Memory latency

- Failure to predict which data items are needed

- Memory bandwidth

- Failure to deliver data at consumption rate of processor

- Load/store instruction issue rate

- Failure of processor to issue enough loads/stores per cycle

- Floating point instruction issue rate

- Low percentage of floating point operations among all operations

# "vertical aspects"

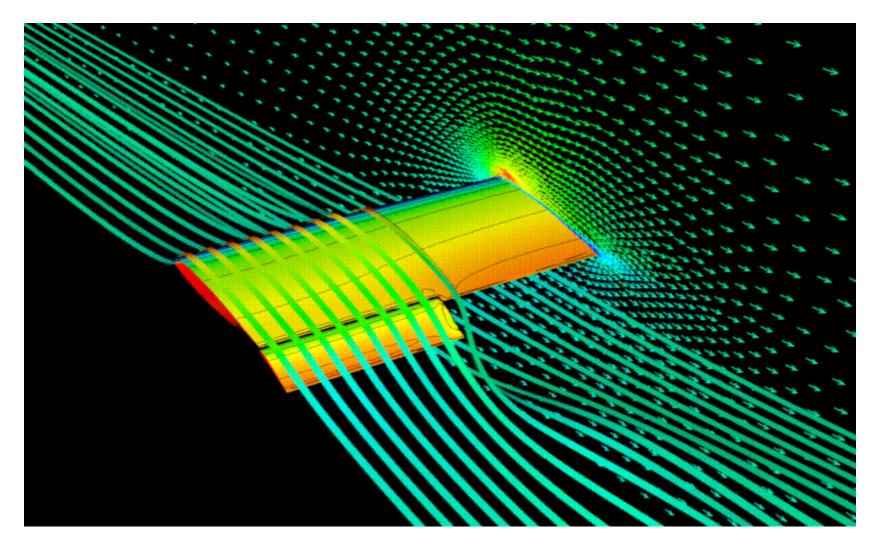

#### **Application Domain:** Computational Aerodynamics

#### **Euler Simulation**

- 3D transonic flow over ONERA M6 wing, at . 3.06° angle of attack (exhibits  $\lambda$ -shock at M = 0.839)

- Solve where

$$\frac{\partial Q}{\partial t} + \frac{1}{V} \oint_{\Omega} (\overrightarrow{F} \cdot \hat{n}) d\Omega = 0$$

$$Q = \begin{bmatrix} \rho \\ \rho u \\ \rho v \\ \rho v \\ \rho w \\ E \end{bmatrix} \quad \vec{F} \cdot \hat{n} = \begin{bmatrix} \rho U \\ \rho U u + \hat{n}_x p \\ \rho U v + \hat{n}_y p \\ \rho U w + \hat{n}_z p \\ (E + p)U \end{bmatrix}$$

$$U = \hat{n}_x u + \hat{n}_y v + \hat{n}_z w$$

$$p = (\gamma - 1) \left[ E - \rho \frac{\left(u^2 + v^2 + w^2\right)}{2} \right]$$

$\rho = \text{density}, u = \text{velocity}, p = \text{pressure}$ E = energy density

DeBenedictis, Keyes, Kogge SC2006 Tutorial

# **Background of FUN3D Application**

- Tetrahedral vertex-centered unstructured grid code developed by W. K. Anderson (NASA) for steady compressible and incompressible Euler and Navier-Stokes

- Used in airplane, automobile, and submarine applications for analysis and design

- Standard discretization is second-order Roe scheme for convection and Galerkin for diffusion

- Newton-Krylov solver with global point-block-ILU preconditioning, with false timestepping for nonlinear continuation towards steady state; competitive with FAS multigrid in practice

- Legacy implementation/ordering is vector-oriented

## **Features of FUN3D Application**

- Based on "legacy" (but contemporary) CFD application with significant F77 code reuse

- Portable, message-passing library-based parallelization, run on NT boxes through Tflop/s ASCI platforms

- Simple multithreaded extension between processors sharing memory physically

- Sparse, unstructured data, implying memory indirection with only modest reuse

- Wide applicability to other implicitly discretized multiple-scale PDE workloads

- Extensive profiling has led to follow-on algorithmic research

# Merits of NKS Algorithm/Implementation

- Relative characteristics: the "exponents" are *naturally* good

- Convergence scalability

- weak (or no) degradation in problem size and parallel granularity (with use of small global problems in Schwarz preconditioner)

- Implementation scalability

- no degradation in ratio of surface communication to volume work (in problem-scaled limit)

- only modest degradation from global operations (for sufficiently richly connected networks)

- Absolute characteristics: the "constants" can be made good

- Operation count complexity

- residual reductions of 10<sup>-9</sup> in 10<sup>3</sup> "work units"

- Per-processor performance

- up to 25% of theoretical peak

- Overall, machine-epsilon solutions require as little as 15 microseconds per degree of freedom!

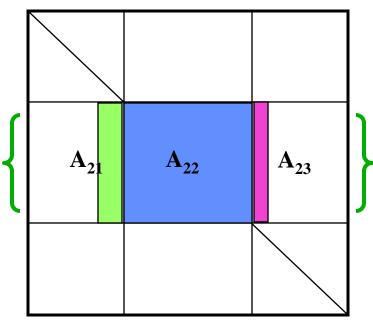

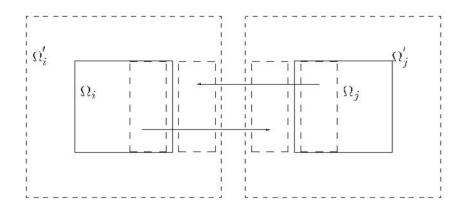

- Form preconditioner *B* out of (approximate) local solves on (overlapping) subdomains

- Let R<sub>i</sub> and R<sub>i</sub><sup>T</sup> be Boolean gather and scatter operations, mapping between a global vector and its i<sup>th</sup> subdomain support

#### **Iteration Count Estimates from the Schwarz Theory**

[ref: Smith, Bjorstad & Gropp, 1996, Camb. Univ. Pr.]

- Krylov-Schwarz iterative methods typically converge in a number of iterations that scales as the square-root of the condition number of the Schwarz-preconditioned system

- In terms of N and P, where for d-dimensional isotropic problems, N=h<sup>-d</sup> and P=H<sup>-d</sup>, for mesh parameter h and subdomain diameter H, iteration counts may be estimated as follows:

| Preconditioning Type     | in 2D                   | in 3D                   |

|--------------------------|-------------------------|-------------------------|

| Point Jacobi             | O(N <sup>1/2</sup> )    | O(N <sup>1/3</sup> )    |

| Domain Jacobi            | O((NP) <sup>1/4</sup> ) | O((NP) <sup>1/6</sup> ) |

| 1-level Additive Schwarz | O(P <sup>1/3</sup> )    | O(P <sup>1/3</sup> )    |

| 2-level Additive Schwarz | O(1)                    | O(1)                    |

# Time-Implicit Newton-Krylov-Schwarz Method

For nonlinear robustness, NKS iteration is wrapped in time-stepping.

```

for (I = 0; I < n \text{ time}; I++) {

select time step

for (k = 0; k < n_Newton; k++) {

compute nonlinear residual and Jacobian

for (j = 0; j < n_Krylov; j++) {

forall (i = 0; i < n_Precon; i++) {

solve subdomain problems concurrently

}

perform preconditioned Jacobian-vector product

enforce Krylov basis conditions

update optimal coefficients

check linear convergence

}

perform DAXPY update

check nonlinear convergence

}

}

Steps in red involve global communication.

```

## **Key Features of Implementation Strategy**

- Subdomain partitioning by one of the MeTiS graph algorithms

- SPMD "owner computes" PETSc implementation under the dual objectives of minimizing the number of messages and overlapping communication with computation

- Each processor "ghosts" its stencil dependences in its neighbors

- Ghost nodes ordered after contiguous owned nodes

- Domain mapped from (user) global ordering into local orderings

- Scatter/gather operations created between *local sequential* vectors and *global distributed* vectors, based on runtime connectivity patterns

- Newton-Krylov-Schwarz operations translated into local tasks and communication tasks

- Profiling used to help eliminate performance bugs in communication and memory hierarchy

# **Background of PETSc**

- Developed by Gropp, Smith, McInnes & Balay (ANL) to support research, prototyping, and production parallel solutions of operator equations in message-passing environments

- Distributed data structures as fundamental objects index sets, vectors/gridfunctions, and matrices/arrays

- Iterative linear and nonlinear solvers, combinable modularly and recursively, and extensibly

- Portable, and callable from C, C++, Fortran

- Uniform high-level API, with multi-layered entry

- Aggressively optimized: copies minimized, communication aggregated and overlapped, caches and registers reused, memory chunks preallocated, inspector-executor model for repetitive tasks (e.g., gather/scatter)

- Now part of the Terascale Optimal PDE Simulations project (DOE SciDAC)

See http://www.mcs.anl.gov/petsc

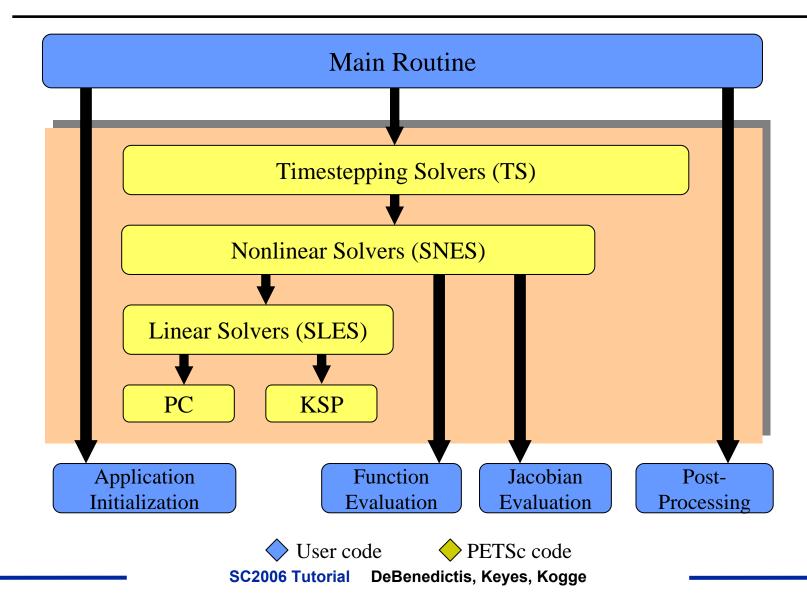

#### Separation of Concerns between User Code and PETSc Library

#### **Outline for PDE Performance Study**

- General characterization of PDE requirements

- Identification of common algorithmic building blocks

- Simple complexity characterizations (computational work, interprocessor communication, intraprocessor data motion)

- Identification and illustration of bottlenecks on some of today's important platforms

- Experiments with a high-performance port of a NASA aerodynamic design code and with a sparse unstructured matrix-vector kernel

- Speculation on useful algorithmic research directions

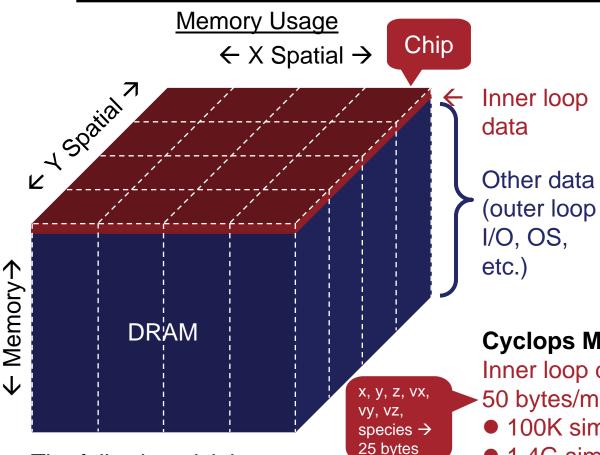

### Variety and Complexity of PDEs

- Varieties of PDEs

- evolution (time hyperbolic, time parabolic)

- equilibrium (elliptic, spatially hyperbolic or parabolic)

- mixed, varying by region

- mixed, of multiple type (e.g., parabolic with elliptic constraint)

- Complexity parameterized by:

- spatial grid points, Nx

- temporal grid points, Nt

- components per point, Nc

- auxiliary storage per point, Na

- grid points in stencil, Ns

- Memory:  $M \approx Nx \bullet (Nc + Na + Nc \bullet Nc \bullet Ns)$

- Work:  $W \approx Nx \bullet Nt \bullet (Nc + Na + Nc \bullet Nc \bullet Ns)$

#### **Explicit Solvers**

$$\mathbf{u}^{l} = \mathbf{u}^{l-1} - \Delta t^{l} \bullet f(\mathbf{u}^{l-1})$$

- Concurrency is pointwise, *O(N)*

- Comm.-to-Comp. ratio is surface-to-volume, O((N/P)<sup>-</sup>

<sup>1/3</sup>)

- Communication range is nearest-neighbor, except for time-step computation

- Synchronization frequency is once per step, O((N/P)<sup>-1</sup>)

- Storage per point is low

- Load balance is straightforward for static quasiuniform grids

- Grid adaptivity (together with temporal stability limitation) makes load balance nontrivial

#### **Domain-decomposed Implicit Solvers**

$$\frac{\mathbf{u}^{l}}{\Delta t^{l}} + f(\mathbf{u}^{l}) = \frac{\mathbf{u}^{l-1}}{\Delta t^{l}}, \Delta t^{l} \to \infty$$

- Concurrency is pointwise, O(N), or subdomainwise, O(P)

- Comm.-to-Comp. ratio still *mainly* surface-tovolume, O((N/P)<sup>-1/3</sup>)

- Communication still *mainly* nearest-neighbor, but nonlocal communication arises from conjugation, norms, coarse grid problems

- Synchronization frequency often more than once per grid-sweep, up to Krylov dimension, O(K(N/P)<sup>-1</sup>)

- Storage per point is higher, by factor of O(K)

- Load balance issues the same as for explicit

## **Resource Scaling for PDEs**

- For 3D problems, work is proportional to four-thirds power of memory, because

- For equilibrium problems, work scales with problem size times number of iteration steps -- proportional to resolution in single spatial dimension

- For evolutionary problems, work scales with problems size times number of time steps -- CFL arguments place latter on order of spatial resolution, as well

- Proportionality constant can be adjusted over a very wide range by both discretization (high-order implies more work per point and per memory transfer) and by algorithmic tuning

- If frequent time frames are to be captured, other resources -disk capacity and I/O rates -- must both scale linearly with work, more stringently than for memory.

- Vertex-based loops

- state vector and auxiliary vector updates

- Edge-based "stencil op" loops

- residual evaluation

- approximate Jacobian evaluation

- Jacobian-vector product (often replaced with matrix-free form, involving residual evaluation)

- intergrid transfer (coarse/fine)

- Sparse, narrow-band recurrences

- approximate factorization and back substitution

- smoothing

- Vector inner products and norms

- orthogonalization/conjugation

- convergence progress and stability checks

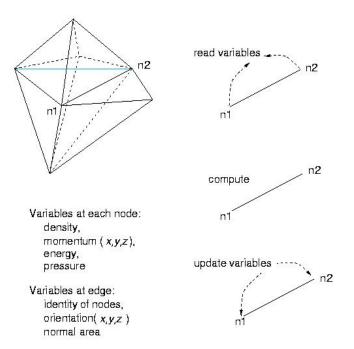

### **Illustration of Edge-based Loop**

- Vertex-centered grid

- Traverse by edges

- load vertex values

- compute intensively

- e.g., for compressible flows, solve 5x5 eigenproblem for characteristic directions and speeds of each wave

- store flux contributions at vertices

- Each vertex appears in approximately 15 flux computations

### **Complexities of PDE Kernels**

- Vertex-based loops

- work and data closely proportional

- pointwise concurrency, no communication

- Edge-based "stencil op" loops

- large ratio of work to data

- colored edge concurrency; local communication

- Sparse, narrow-band recurrences

- work and data closely proportional

- frontal concurrency; no, local, or global communication

- Vector inner products and norms

- work and data closely proportional

- pointwise concurrency; global communication

### Candidate stresspoints of PDE kernels

- Vertex-based loops

- memory bandwidth

- Edge-based "stencil op" loops

- load/store (register-cache) bandwidth

- internode bandwidth

- Sparse, narrow-band recurrences

- memory bandwidth

- internode bandwidth, internode latency, network diameter

- Inner products and norms

- memory bandwidth

- internode latency, network diameter

#### **Observation #1:**

Processor scalability no problem, in principle

- As popularized with the 1986 Karp Prize paper of Benner, Gustafson & Montry, Amdahl's law can be defeated if serial (or bounded concurrency) sections make up a decreasing fraction of total work as problem size and processor count scale --- true for most iterative implicit nonlinear PDE solvers

- Simple, back-of-envelope parallel complexity analyses show that processors can be increased as fast, or almost as fast, as problem size, assuming load is perfectly balanced

- Caveat: the processor network must also be scalable (applies to protocols as well as to hardware); machines based on common bus networks will not scale

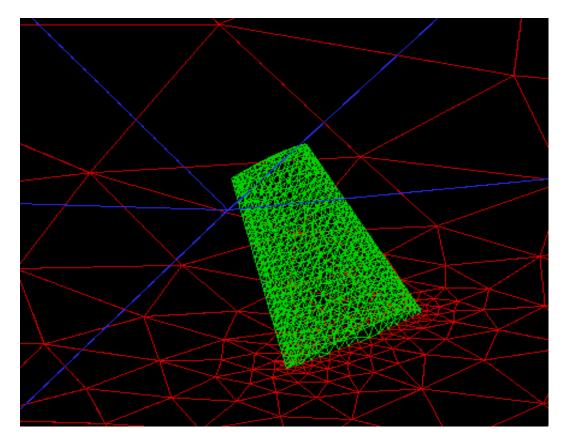

• 2.8 M vertices in the actual computational domain (9K in image below)

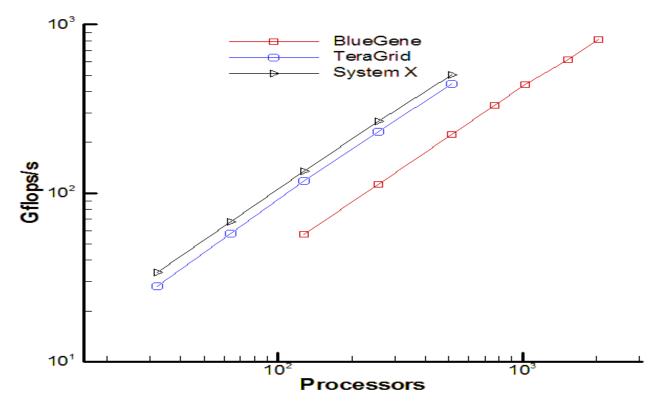

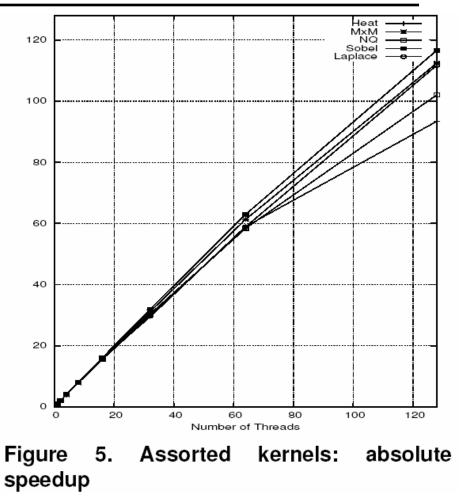

### **Parallel Performance of PETSc-FUN3D**

3D Mesh: 2,761,774 Vertices and 18,945,809 Edges TeraGrid: Dual 1.5 GHz Intel Madison Processors with 4 MB L2 Cache BlueGene: Dual 700 MHz IBM Processors with 4 MB L3 Cache System X: Dual 2.3 GHz PowerPC 970FX processors with 0.5 MB L2 Cache

SC2006 Tutorial DeBenedictis, Keyes, Kogge

### Fixed-size Parallel Scaling Results (Flop/s)

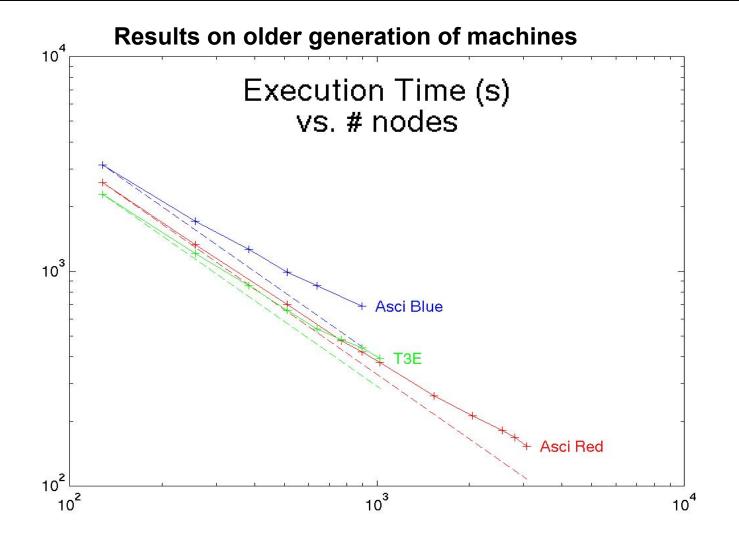

#### **Results on older generation of machines**

SC2006 Tutorial DeBenedictis, Keyes, Kogge

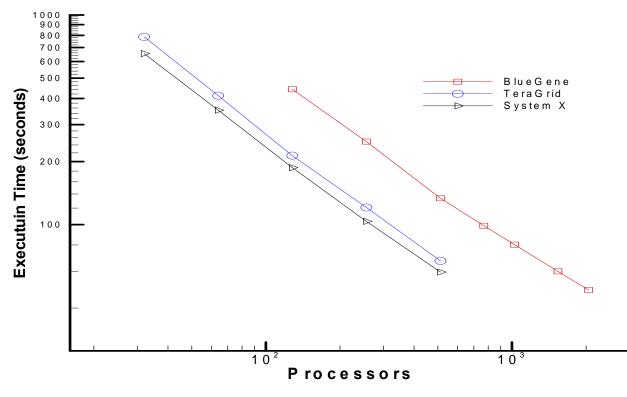

### **Parallel Performance of PETSc-FUN3D**

3D Mesh: 2,761,774 Vertices and 18,945,809 Edges TeraGrid: Dual 1.5 GHz Intel Madison Processors with 4 MB L2 Cache BlueGene: Dual 700 MHz IBM Processors with 4 MB L3 Cache System X: Dual 2.3 GHz PowerPC 970FX processors with 0.5 MB L2 Cache

SC2006 Tutorial DeBenedictis, Keyes, Kogge

#### Fixed-size Parallel Scaling Results (seconds)

SC2006 Tutorial DeBenedictis, Keyes, Kogge

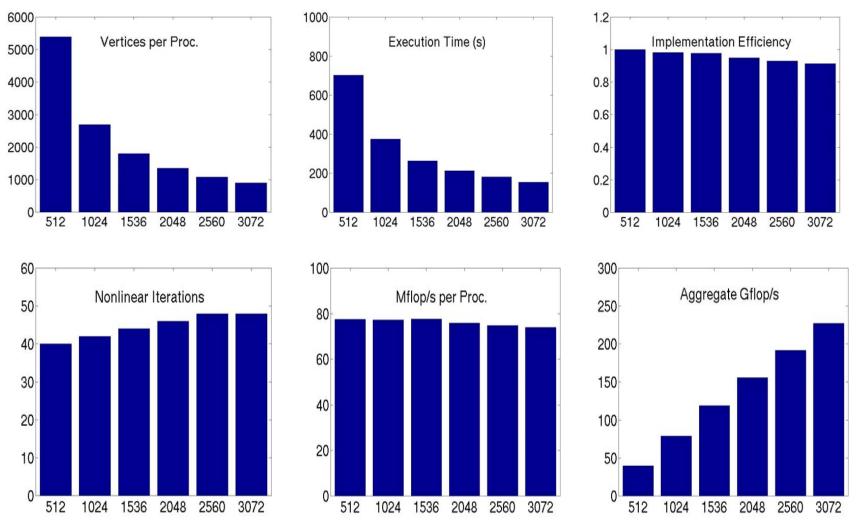

#### Inside Parallel Scaling Results on ASCI Red

ONERA M6 Wing Test Case, Tetrahedral grid of 2.8 million vertices (about 11 million unknowns) on up to 3072 ASCI Red nodes (each with dual Pentium Pro 333 MHz processors)

SC2006 Tutorial DeBenedictis, Keyes, Kogge

#### Observation #2 (for Fixed-Size Problems): Synchronization eventually a bottleneck

- Percentage of time spent in communication phases on ASCI Red for NKS unstructured Euler simulation

- Principal nonscaling feature is synchronization at global inner products and norms, while cost of halo exchange grows slowly even for fixed-size problem with deteriorating surface-to-volume

| Number of<br>Processors | Global<br>reductions | Synchronizations | Halo<br>Exchanges |

|-------------------------|----------------------|------------------|-------------------|

| 128                     | 5%                   | 4%               | 3%                |

| 256                     | 3%                   | 6%               | 4%                |

| 512                     | 3%                   | 7 %              | 5%                |

| 768                     | 3%                   | 8%               | 5%                |

| 1024                    | 3%                   | 10%              | 6 %               |

#### **Observation #3:**

#### Memory latency no problem, in principle

- Regularity of reference in static grid-based computations can be exploited through memory-assist features to cover latency

- PDEs have simple, periodic workingset structure that permits effective use of prefetch/dispatch directives, and lots of slackness (process concurrency in excess of hardware concurrency)

- Combined with coming processors-in-memory (PIM) technology for gather/scatter into densely used block transfers and multithreading for latency that cannot be amortized by sufficiently large block transfers, the solution of PDEs can approach zero stall conditions

- Caveat: high bandwidth is critical to covering latency

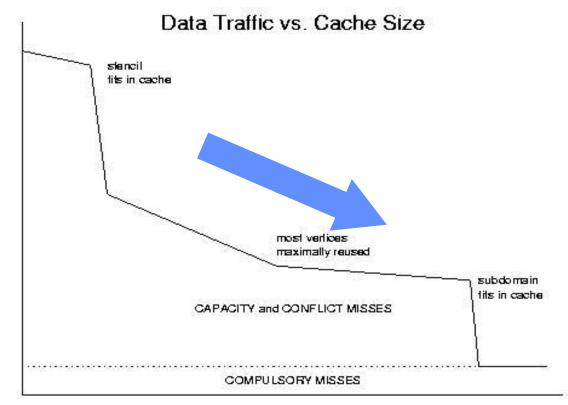

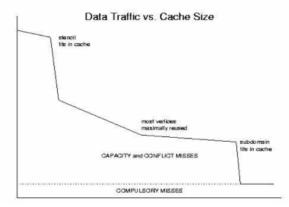

#### **Workingset Characterization of Memory Traffic**

- Smallest: data for single stencil

- Largest: data for entire subdomain

- Intermediate: data for a neighborhood collection of stencils, reused as many times as possible

### Thought Experiment: Cache Traffic for PDEs

As successive workingsets ``drop" into a level of memory, capacity (and with effort conflict) misses disappear, leaving only compulsory, reducing demand on main memory bandwidth

### **BW-stretching Strategies Based on Workingsets**

- No performance value in memory levels larger than subdomain

- Little performance value in memory levels smaller than subdomain but larger than required to permit full reuse of most data within each subdomain subtraversal (middle knee, prev. slide)

- After providing L1 large enough for smallest workingset (and multiple independent copies up to desired level of multithreading, if necessary all additional resources should be invested in large L2

- Tables describing grid connectivity are built (after each grid rebalancing) and stored in PIM --- used to pack/unpack dense-use cache lines during subdomain traversal

### **Three Types of Locality Enhancements**

- *Edge-reordering* for maximal vertex reuse

- Field interlacing for maximal cache-line reuse

- use U1, V1, W1, U2, V2, W2, ..., Un, Vn, Wn

- rather than U1, U2, ..., Un, V1, V2, ..., Vn, W1, W2, ..., Wn

- Sparse Jacobian blocking for minimal integer metadata in manipulating a given amount of floating point physical data

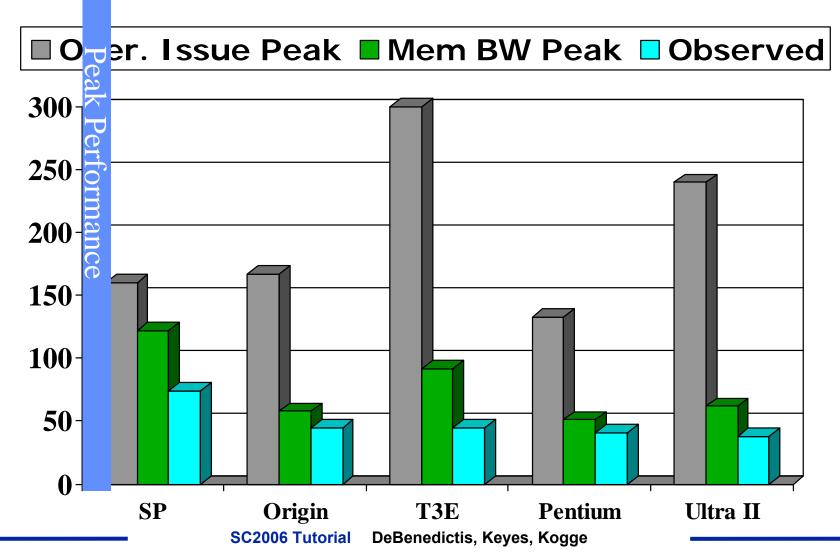

#### **Improvements Resulting from Locality Reordering**

| Processor     | Clock<br>MHz | Peak<br>Mflop/s | Opt.<br>% of<br>Peak | Opt.<br>Mflop/s | Reord.<br>Only<br>Mflop/s | Interl.<br>only<br>Mflop/s | Orig.<br>Mflop/s | Orig.<br>% of Peak |

|---------------|--------------|-----------------|----------------------|-----------------|---------------------------|----------------------------|------------------|--------------------|

| R10000        | 250          | 500             | 25.4                 | 127             | 74                        | 59                         | 26               | 5.2                |

| Р3            | 200          | 800             | 20.3                 | 163             | 87                        | 68                         | 32               | 4.0                |

| P2SC (2 card) | 120          | 480             | 21.4                 | 101             | 51                        | 35                         | 13               | 2.7                |

| P2SC (4 card) | 120          | 480             | 24.3                 | 117             | 59                        | 40                         | 15               | 3.1                |

| 604e          | 332          | 664             | 9.9                  | 66              | 43                        | 31                         | 15               | 2.3                |

| Alpha 21164   | 450          | 900             | 8.3                  | 75              | 39                        | 32                         | 14               | 1.6                |

| Alpha 21164   | 600          | 1200            | 7.6                  | 91              | 47                        | 37                         | 16               | 1.3                |

| Ultra II      | 300          | 600             | 12.5                 | 75              | 42                        | 35                         | 18               | 3.0                |

| Ultra II      | 360          | 720             | 13.0                 | 94              | 54                        | 47                         | 25               | 3.5                |

| Ultra II/HPC  | 400          | 800             | 8.9                  | 71              | 47                        | 36                         | 20               | 2.5                |

| Pent. II/LIN  | 400          | 400             | 20.8                 | 83              | 52                        | 47                         | 33               | 8.3                |

| Pent. II/NT   | 400          | 400             | 19.5                 | 78              | 49                        | 49                         | 31               | 7.8                |

| Pent. Pro     | 200          | 200             | 21.0                 | 42              | 27                        | 26                         | 16               | 8.0                |

| Pent. Pro     | 333          | 333             | 18.8                 | 60              | 40                        | 36                         | 21               | 6.3                |

#### **Observation #4:**

Memory bandwidth a major bottleneck

Execution times for NKS Euler Simulation on Origin 2000: (standard) double precision matrices versus single precision

| Number of<br>Processors | Computational Phase |           |        |        |  |

|-------------------------|---------------------|-----------|--------|--------|--|

|                         | Line                | ear Solve | 0      | verall |  |

|                         | Double              | Single    | Double | Single |  |

| 16                      | 223s                | 136s      | 746s   | 657s   |  |

| 32                      | 117s                | 67s       | 373s   | 331s   |  |

| 64                      | 60s                 | 34s       | 205s   | 181s   |  |

| 120                     | 31s                 | 16s       | 122s   | 106s   |  |

Note that times are nearly halved, along with precision, for the BW-limited linear solve phase, indicating that the BW can be at least doubled before hitting the next bottleneck!

### **ASCI Memory Bandwidth Bottleneck**

- Per-processor memory bandwidth versus rate of work

- approximately 10-15 flops per word transferred from memory

- fairly constant across machines, and fairly poor without extensive reuse

|          | Peak<br>(MF/s) | BW/proc<br>(MW/s) | (MF/s)/<br>(MW/s) |

|----------|----------------|-------------------|-------------------|

| White    | 1500           | 125.0             | 12.0              |

| Blue Mtn | 500            | 48.8              | 10.2              |

| Blue Pac | 666            | 45.0              | 14.8              |

| Red      | 333            | 33.3              | 10.0              |

Implications of Bandwidth Limitations in Shared Memory Systems

- The processors on a node compete for the available memory bandwidth

- The computational phases that are memory bandwidth limited will not scale and may even run slower due to arbitration

- Stream Benchmark on ASCI Red MB/s for the Triad Operation

| Vector Size | 1 Thread | 2 Threads |

|-------------|----------|-----------|

| 1E04        | 666      | 1296      |

| 5E04        | 137      | 238       |

| 1E05        | 140      | 144       |

| 1E06        | 145      | 141       |

| 1E07        | 157      | 152       |

Larger vectors in last three rows do not fit into cache and are bandwidth-limited

## BW-stretching Strategies

### **Based on Multivectors in Sparse Matvecs**

- The sparse matrix-vector multiply (matvec) is one of the most common kernels in scientific computing

- Same data access considerations as stencil-op kernel in explicit methods for PDEs

- Same as Krylov kernel and similar to preconditioner application kernel in implicit methods for PDEs

- When multiplying a single vector, each element of the sparse matrix is used exactly once per matvec

- If the matrix is large, none of its elements will remain in the cache from one matvec to the next

- If multiple vectors, say *N*, are multiplied at once, each element of the matrix is reused *N* times

- A simple complexity model for the sparse matrix-vector product illustrates the issues

### Matrix-vector Multiplication for a Single Vector

This version performs  $A \times x$

```

do i = 1, n

fetch ia(i+1)

! loop over the non-zeros of the row

do j = ia(i), ia(i + 1) - 1

fetch ja(j), a(j), x<sub>1</sub>(ja(j)), .....x<sub>N</sub>(ja(j))

do N fmadd (floating multiply add)

enddo

Store y_1(i) \dots y_N(i)

```

enddo

This version performs A  $\times$  {x<sub>1</sub>, ..., x<sub>N</sub>}

### **Estimating the Memory Bandwidth Limitation**

- Assume ideal memory system apart from bandwidth

- Perfect cache (only compulsory misses; no overhead)

- No memory latency

- Unlimited number of loads and stores per cycle

- Specify number of rows and nonzeros, sizes for integers and floats

- Assume matrix blocking factor and vector blocking factor

- Compute data volume associated with sparse matvec

- Compute number of floating-point multiply adds (fmadd)

- Bytes per floating multiply-add combined with memory bandwidth (bytes/second) give a bound on rate of execution of multiply-adds

#### **Sparse Matvec Performance Summary**

- On 250 MHz MIPS R10000

- Matrix size = 90,708; number of nonzero entries = 5,047,120, blocksize = 4

- Stream performance is 358 MB/sec (for triad vector operation) <u>http://www.cs.virginia.edu/stream</u>

- Number of Vectors is either 1 or a block of 4

| Format Number of |         |       | Bandwidth |          | MFlops |          |

|------------------|---------|-------|-----------|----------|--------|----------|

| Format           | Vectors | fmadd | Required  | Achieved | Ideal  | Achieved |

| AIJ              | 1       | 12.36 | 3090      | 276      | 58     | 45       |

| AIJ              | 4       | 3.31  | 827       | 221      | 216    | 120      |

| BAIJ             | 1       | 9.31  | 2327      |          | 84     | 55       |

| BAIJ             | 4       | 2.54  | 635       | 229      | 305    | 175      |

• Ratio of 2.7 for **AIJ** and 3.2 for **BAIJ** in going from 1 to 4

#### Performance Summary on 2.4 GHz P4 Xeon

- Matrix size, n = 90,708; number of nonzero entries, N<sub>nz</sub> = 5,047,120 (from computational aerodynamics, b=4)

- Stream performance is 1973 MB/sec (for triad vector operation, <u>http://www.cs.virginia.edu/stream</u>)

- Number of Vectors, N = 1, and 4

| Format | Number of | Bytes / | Bandwid  | Bandwidth (GB/s) |       | MFlops   |  |

|--------|-----------|---------|----------|------------------|-------|----------|--|

| ronnat | Vectors   | flop    | Required | Measured         | Ideal | Achieved |  |

| AIJ    | 1         | 6.18    | 14.83    | 1.97             | 319   | 274      |  |

| AIJ    | 4         | 1.66    | 3.98     | 1.97             | 1188  | 615      |  |

#### Comparison of Domain-Level Parallelism for MPI and OpenMP/MPI

• Table shows execution times of residual flux evaluation phase for W-cycle FAS Euler simulation on ASCI Red (2 processors per node)

• Thread management imposes an overhead of 5% up to more serious levels, depending upon the system

• In computational phases that are not memory bandwidth-limited, shared-memory multithreading can be more efficient than MPI-mediated domain-based multiprocessing

| # Nodes | On each node     | Sec./W-cycle |

|---------|------------------|--------------|

| 128     | 1 MPI process    | 14.01        |

| 128     | 2 MPI processes  | 7.98         |

| 128     | 2 OpenMP threads | 7.56         |

| 256     | 1 MPI process    | 7.59         |

#### **Observation #5:**

#### Load-store functionality may be a bottleneck

• Table shows execution times of residual flux evaluation phase for NKS Euler simulation on ASCI Red (2 processors per node)

- In each paradigm, the second processor per node contributes another load/store unit while sharing fixed memory bandwidth

- Note that 1 thread is worse than 1 MPI process, but that 2-thread performance eventually surpass 2-process performance as subdomains become small

| Nodes | MPI/O | penMP | MPI    |        |

|-------|-------|-------|--------|--------|

|       | 1 Thr | 2 Thr | 1 Proc | 2 Proc |

| 256   | 483s  | 261s  | 456s   | 258s   |

| 2560  | 76s   | 39s   | 72s    | 45s    |

| 3072  | 66s   | 33s   | 62s    | 40s    |

### **Quantifying the Load/Store Bottleneck**

- Assume ideal memory system apart from load/store units

- All data items are ready in cache

- Each operation takes only one cycle to complete but multiple operations can graduate in one cycle

- If only one load or store can be issued in one cycle (as is the case on R10000 and many other processors), the best we can hope for is

Number of floating point instructions Number of Loads and Stores \*Peak MFlops/s

Other restrictions (like primary cache latency, latency of floating point units etc.) need to be taken into account while creating the best schedule

#### Observation #6: Fraction of Flops may be a Bottleneck

AT:address transln; Br: branch; Iop: integer op; Flop: floating point op; Of: offset calculation; Ld: load; St: store

• Estimated number of floating point operations out of the total instructions (for the unstructured Euler Jacobian)

$$-$$

**For**  $N=1$ ,  $I_f = 0.18$

- For N = 4,  $I_f = 0.34$ ; this is one-third of peak

### Significance of Multivectors

- Using multivectors can improve the performance of sparse matrix-vector product significantly

- "Algorithmic headroom" is available for modest blocking

- Simple models predict the performance of sparse matrix-vector operations on a variety of platforms, including the effects of *memory bandwidth*, and *instruction issue* rates

- achievable performance is a small fraction of stated peak for sparse matrix-vector kernels, independent of code quality

- compiler improvements and intelligent prefetching can help but the problem is fundamentally an architecturealgorithm mismatch and needs an algorithmic solution

#### **Realistic Measures of Performance**

Sparse Matrix Vector Product one vector, matrix size = 90,708, nonzero entries = 5,047,120

- Processor scalability is no problem, in principle

- Common bus-based network is a bottleneck

- For fixed-size problems, global synchronization is eventually a bottleneck

- Memory latency is no problem, in principle

- Memory bandwidth is a *major* bottleneck

- Load-Store functionality *may* be a bottleneck

- Frequency of floating point instructions may be a bottleneck

### **Lessons for High-end Simulation of PDEs**

- Unstructured (static) grid codes can run well on distributed hierarchical memory machines, with attention to partitioning, vertex ordering, component ordering, blocking, and tuning

- Parallel solver libraries can give new life to the most valuable, discipline-specific modules of legacy PDE codes

- Parallel scalability is easy, but attaining high per-processor performance for sparse problems gets more challenging with each machine generation

- The NKS family of algorithms can be and must be tuned to an application-architecture combination; profiling is critical

- Some gains from hybrid parallel programming models (message passing and multithreading together) require little work; squeezing the last drop is likely much more difficult

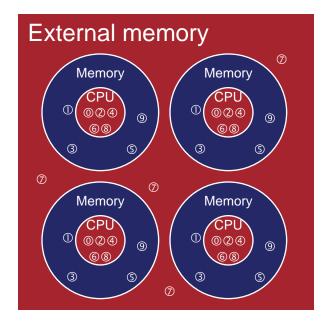

### Weighing in at the Bottom Line

- Characterization of a 1 Teraflop/s computer of today

- about 1,000 processors of 1 Gflop/s (peak) each

- due to inefficiencies within the processors, more practically characterized as about 4,000 processors of 250 Mflop/s each

- How do we want to get to 1 Petaflop/s?

- 1,000,000 processors of 1 Gflop/s each (only wider)?

- 10,000 processors of 100 Gflop/s each (mainly deeper)?

- From the point of view of PDE simulations on quasi-static Eulerian grids

- Either!

- Caveat: dynamic grid simulations are not directly covered in this discussion

- but see work 2003 SIAM/ACM Prize

# Some noteworthy algorithmic adaptations U to distributed memory architecture

- Restricted Schwarz in elliptic problems (Cai & Sarkis)

- omit every other local communication (actually leads to better convergence, now proved)

- Extrapolated Schwarz in parabolic problems (Garbey & Tromeur-Dervout)

- hide interprocessor latency by extrapolating messages received in time integration, with rollback if actual messages have discrepancies in lower Fourier modes (higher mode discrepancies decay anyway)

- Nonlinear Schwarz in elliptic problems (Cai & Keyes)

- reduce global Krylov-Schwarz synchronizations by applying NKS within well-connected subdomains and performing *few* global outer Newton iterations

- Aggressive coarsening in linear AMG (Falgout, Yang, et al.)

- reduce size of coarse problems to trade-off cost per iteration with number of iterations (and many other such preconditioner quality ideas)

### Four Sources of Performance Improvement

- Expanded number of processors

- arbitrarily large factor, through extremely careful attention to load balancing and synchronization

- More efficient use of processor cycles, and faster processor/memory elements

- one to two orders of magnitude, through memoryassist language features, processors-in-memory, and multithreading

- Algorithmic variants that are more architecture-friendly

- approximately an order of magnitude, through improved locality and relaxed synchronization

- Algorithms that deliver more "science per flop"

- possibly large problem-dependent factor, through adaptivity

- This last does not contribute to raw flop/s!

### Source #1:

**Expanded Number of Processors**

- Recall Observation #1 and "back-of-envelope estimates": Scalability not a problem.

- Caveat: the processor network must also be scalable (applies to protocols as well as to hardware)

- Remaining four orders of magnitude could be met by hardware expansion (but this does *not* mean that fixed-size applications of today would run 10<sup>4</sup> times faster)

### Source #2:

### More Efficient Use of Faster Processors

- Current low efficiencies of sparse codes can be improved if regularity of reference is exploited with memory-assist features

- Recall Observation #3: PDEs have exploitable periodic workingset structures that can overcome memory latency

- Caveat: high bandwidth is critical, since PDE algorithms do only O(N) work for O(N) gridpoints worth of loads and stores

- One to two orders of magnitude can be gained by catching up to the clock, and by following the clock into the few-GHz range

### Source #3:

### More "Architecture Friendly" Algorithms

- Algorithmic practice needs to catch up to architectural demands

- several "one-time" gains remain to be contributed that could improve data locality or reduce synchronization frequency, while maintaining required concurrency and slackness

- "One-time" refers to improvements by small constant factors, nothing that scales in *N* or *P* – complexities are already near information-theoretic lower bounds, and we reject increases in flop rates that derive from *less* efficient algorithms

- Caveat: remaining algorithmic performance improvements may cost extra space or may bank on stability shortcuts that occasionally backfire, making performance modeling less predictable

- Perhaps an order of magnitude of performance remains here

### **Raw Performance Improvement from Algorithms**

- Spatial reorderings that improve locality

- interlacing of all related grid-based data structures

- ordering gridpoints and grid edges for L1/L2 reuse

- Discretizations that improve locality

- higher-order methods (lead to larger denser blocks at each point than lower-order methods)

- vertex-centering (for same tetrahedral grid, leads to denser blockrows than cell-centering)

- Temporal reorderings that improve locality

- block vector algorithms (reuse cached matrix blocks; vectors in block are independent)

- multi-step vector algorithms (reuse cached vector blocks; vectors have sequential dependence)

### Raw Performance Improvement from Algorithms, cont.

- Temporal reorderings that reduce synchronization penalty

- less stable algorithmic choices that reduce synchronization frequency (deferred orthogonalization, speculative step selection)

- less global methods that reduce synchronization range by replacing a tightly coupled global process (e.g., Newton) with loosely coupled sets of tightly coupled local processes (e.g., Schwarz)

- Precision reductions that make bandwidth seem larger

- lower precision representation of preconditioner matrix coefficients or poorly known coefficients (arithmetic is still performed on full precision extensions)

### Source #4:

### **Algorithms Packing More Science Per Flop**

- Some algorithmic improvements do not improve flop rate, but lead to the same scientific end in the same time at lower hardware cost (less memory, lower operation complexity)

- Caveat: such adaptive programs are more complicated and less thread-uniform than those they improve upon in quality/cost ratio

- Desirable that petaflop/s machines be general purpose enough to run the "best" algorithms

- Not daunting, conceptually, but puts an enormous premium on dynamic load balancing

- An order of magnitude or more can be gained here for many problems

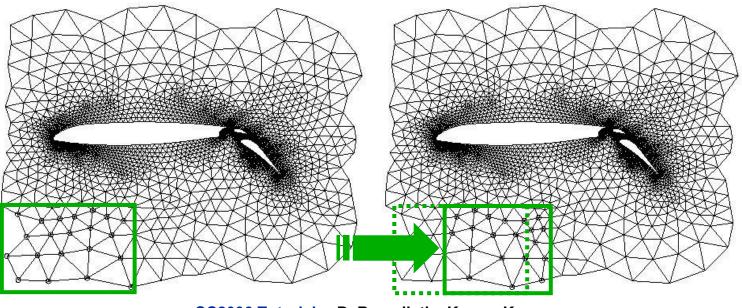

### **Example of Adaptive Opportunities**

- Spatial Discretization-based adaptivity

- change discretization type and order to attain required approximation to the continuum everywhere without overresolving in smooth, easily approximated regions

- Fidelity-based adaptivity

- change continuous formulation to accommodate required phenomena everywhere without enriching in regions where nothing happens

- Stiffness-based adaptivity

- change solution algorithm to provide more powerful, robust techniques in regions of space-time where discrete problem is linearly or nonlinearly stiff without extra work in nonstiff, locally well-conditioned regions

- Metrics and procedures well developed in only a few areas

- method-of-lines ODEs for stiff IBVPs and DAEs, FEA for elliptic BVPs

- Multi-model methods used in *ad hoc* ways in production

- Boeing TRANAIR code

- Poly-algorithmic solvers demonstrated in principle but rarely in the "hostile" environment of high-performance computing

- Requirements for progress

- management of hierarchical levels of synchronization

- user specification of hierarchical priorities of different threads

### Summary of Suggestions for High Performance

- Algorithms that deliver more "science per flop"

- possibly large problem-dependent factor, through adaptivity (but we won't count this towards rate improvement)

- Algorithmic variants that are more architecture-friendly

- expect half an order of magnitude, through improved locality and relaxed synchronization

- More efficient use of processor cycles, and faster processor/memory

- expect one-and-a-half orders of magnitude, through memory-assist language features, PIM, and multithreading

- Expanded number of processors

- expect *two* orders of magnitude, through dynamic balancing and extreme care in implementation

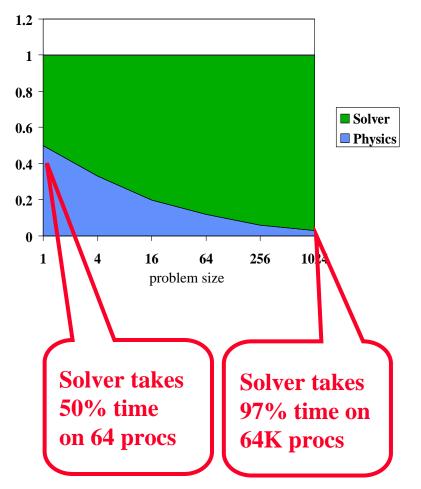

### It's not about the solver

### It's all about the solver (at the terascale)

- Given, for example:

- a "physics" phase that scales as O(N)

- a "solver" phase that scales as O(N<sup>3/2</sup>)

- computation is almost all solver after several doublings

- Most applications groups have not yet "felt" this curve in their gut

- BG/L will change this

- 64K-processor machine delivered in 2005

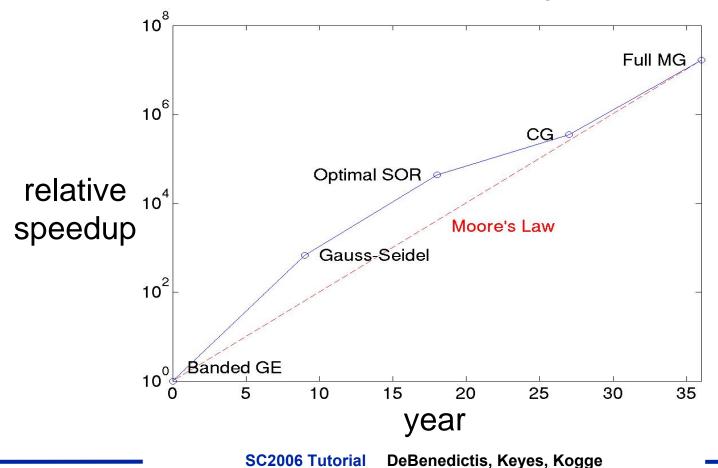

### The power of optimal algorithms

- Advances in algorithmic efficiency can rival advances in hardware architecture

- Consider Poisson's equation on a cube of size N=n<sup>3</sup>

| Year | Method      | Reference                  | Storage        | Flops                  |                       |

|------|-------------|----------------------------|----------------|------------------------|-----------------------|

| 1947 | GE (banded) | Von Neumann &<br>Goldstine | n <sup>5</sup> | <b>n</b> <sup>7</sup>  | 64 64                 |

| 1950 | Optimal SOR | Young                      | n <sup>3</sup> | n <sup>4</sup> log n   | $\nabla^2 u = f$ > 64 |

| 1971 | CG          | Reid                       | n <sup>3</sup> | n <sup>3.5</sup> log n | N                     |

| 1984 | Full MG     | Brandt                     | n <sup>3</sup> | <i>n</i> <sup>3</sup>  |                       |

If n=64, this implies an overall reduction in flops of ~16 million

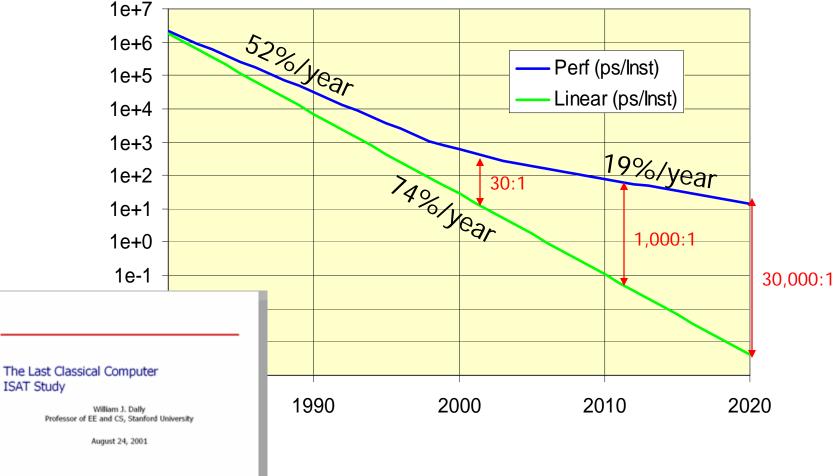

### Algorithms and Moore's Law

- This advance took place over a span of about 36 years, or 24 doubling times for Moore's Law

- $2^{24} \approx 16$  million  $\Rightarrow$  the same as the factor from algorithms alone!

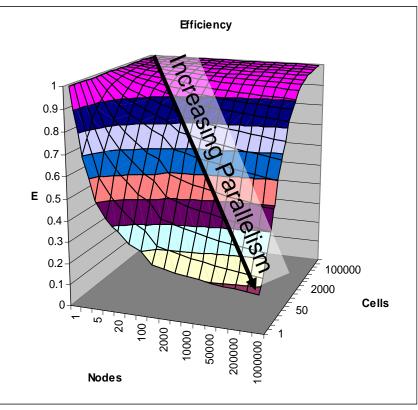

### Algebraic multigrid on BG/L

- Algebraic multigrid a key algorithmic technology

- Discrete operator defined for finest grid by the application, itself, and for many recursively derived levels with successively fewer degrees of freedom, for solver purposes

- Unlike geometric multigrid, AMG not restricted to problems with "natural" coarsenings derived from grid alone

- Optimality (cost per cycle) intimately tied to the ability to coarsen aggressively

- Convergence scalability (number of cycles) and parallel efficiency also sensitive to rate of coarsening

While much research and development remains, multigrid will clearly be practical at BG/L-scale concurrency

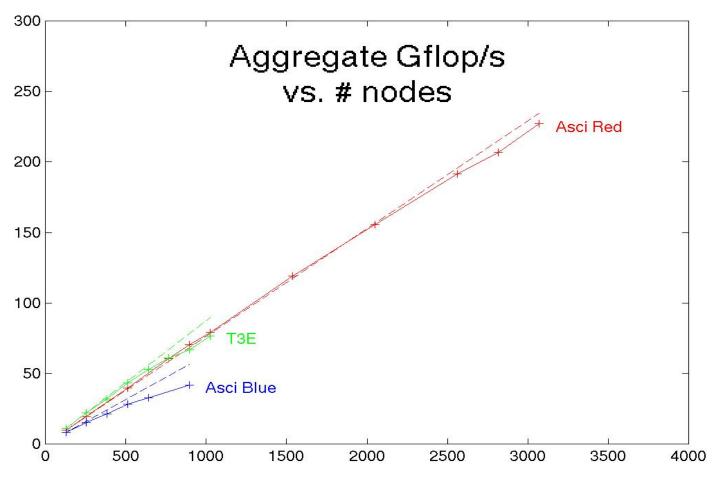

Figure shows weak scaling result for AMG out to 131,072 processors, with one  $25 \times 25 \times 25$  block per processor (from 15.6K dofs up to 2.05B dofs)

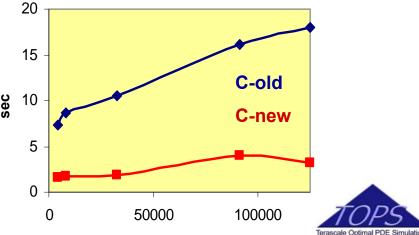

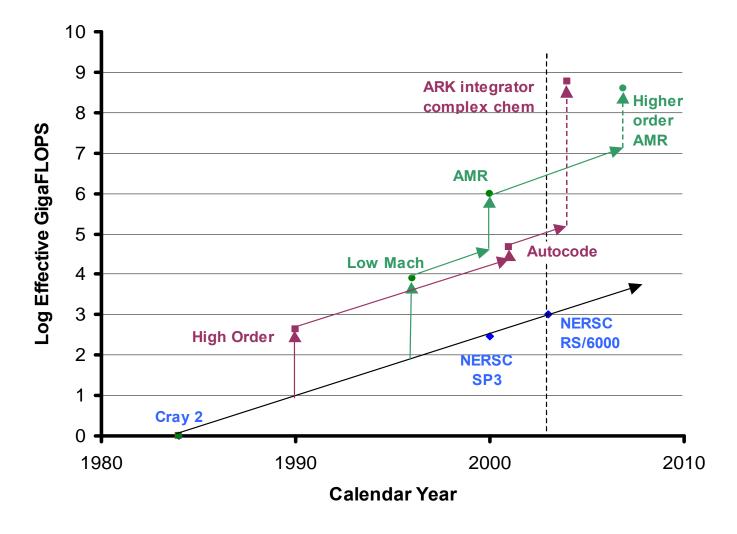

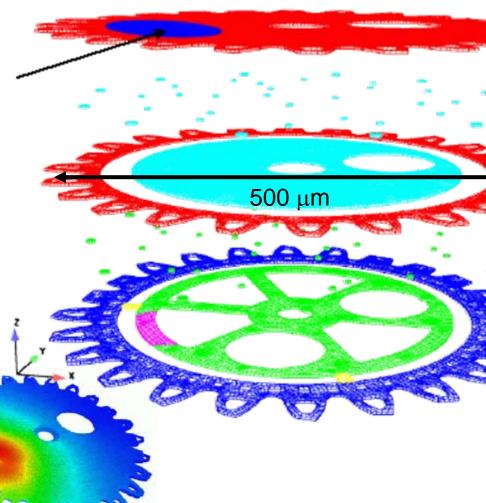

### "Moore's Law" for combustion simulations

Figure from SCaLeS report, VSC20862Tutorial DeBenedictis, Keyes, Kogge

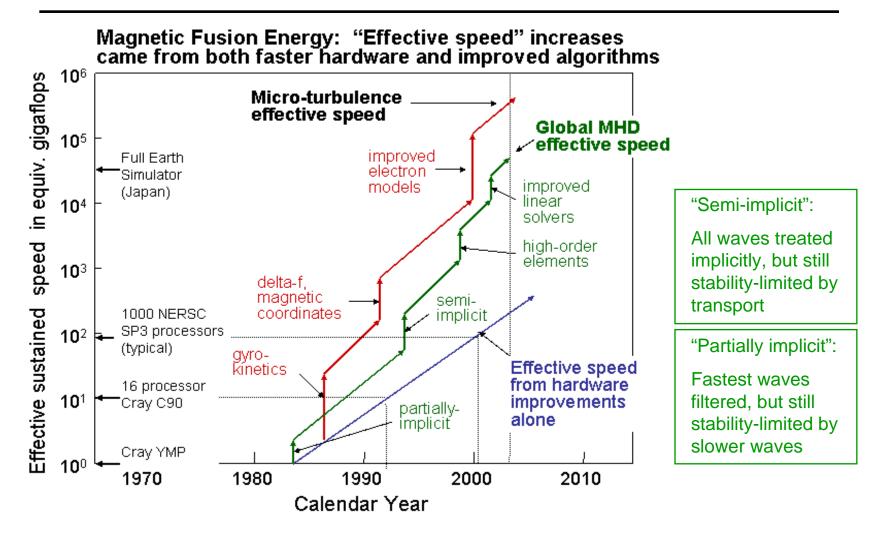

"Moore's Law" for MHD simulations

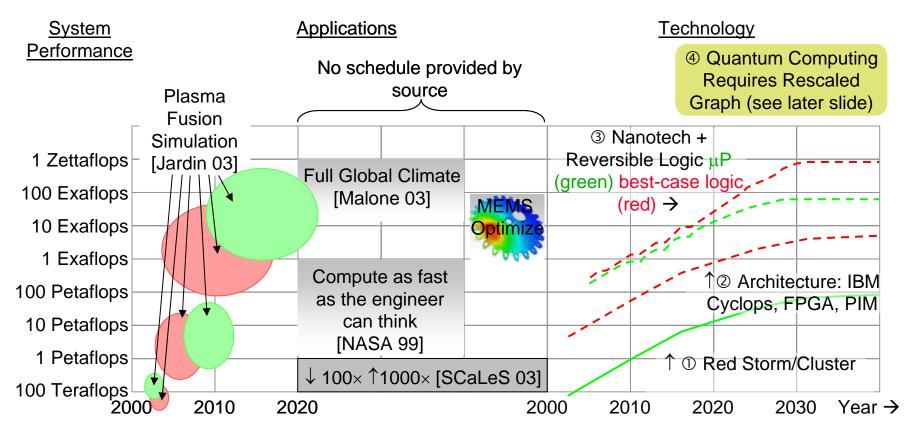

### Scaling fusion simulations up to ITER

| name                | symbol                                                   | units  | CDX-U                   | DIII-D              | ITER                |  |  |

|---------------------|----------------------------------------------------------|--------|-------------------------|---------------------|---------------------|--|--|

| Field               | B <sub>0</sub>                                           | Tesla  | 0.22                    | 1                   | 5.3                 |  |  |

| Minor<br>radius     | а                                                        | meters | .22                     | .67                 | 2                   |  |  |

| Temp.               | $T_{e}$                                                  | keV    | 0.1                     | 2.0                 | 8.                  |  |  |

| Lundquist<br>no.    | S                                                        |        | 1×10 <sup>4</sup>       | 7×10 <sup>6</sup>   | 5×10 <sup>8</sup>   |  |  |

| Mode<br>growth time | $\tau_A S^{1/2}$                                         | s      | 2×10-4                  | 9×10 <sup>-3</sup>  | 7×10-2              |  |  |

| Layer<br>thickness  | aS <sup>-1/2</sup>                                       | m      | 2×10 <sup>-3</sup>      | 2×10-4              | 8×10 <sup>-5</sup>  |  |  |

| zones               | $N_{R}\!\!\times\!\!N_{\theta}\!\!\times\!\!N_{\varphi}$ |        | 3×10 <sup>6</sup>       | 5×10 <sup>10</sup>  | 3×10 <sup>13</sup>  |  |  |

| CFL<br>timestep     | $\Delta X/V_A$<br>(Explicit)                             | s      | 2×10 <sup>-9</sup>      | 8×10 <sup>-11</sup> | 7×10 <sup>-12</sup> |  |  |

| Space-<br>time pts  |                                                          |        | 6×10 <sup>12</sup>      | 1×10 <sup>20</sup>  | 6×10 <sup>24</sup>  |  |  |

|                     |                                                          |        | 10 <sup>12</sup> needed |                     |                     |  |  |

International Thermonuclear **Experimental Reactor**

2017 – first experiments, in Cadaraches, France

Hardware

0

Software:

- PDEs continue to drive the highest-end computing, as they have since ca. 1945

- There appears to be no fundamental limit to solving PDEs on arbitrarily fine spatial meshes in fixed execution time with arbitrarily high numbers of processors provided...

- one does not have to resolve timescales correspondingly finely in a CFL sense

- one can do a very fine load balancing and amortize it over many steps

- one has a near optimal linear implicit solver, like Krylov-MG

- for nonlinear problems, one can use Newton in a resolution-independent asymptotic regime

- One should expect to have to *work!* to achieve such ends, and should start with good solver components as building blocks

### Reminder about the Source of Simulations

- Computational science and engineering is not about individual large-scale analyses, done fast and "thrown over the wall"

- Both "results" and their sensitivities are desired; often multiple operation points to be simulated are known *a priori*, rather than sequentially

- Sensitivities may be fed back into optimization process

- Full CFD analyses may also be inner iterations in a multidisciplinary computation

- In such contexts, "petaflop/s" may mean 1,000 analyses running somewhat asynchronously with respect to each other, each at 1 Tflop/s – clearly a less daunting challenge and one that has better synchronization properties for exploiting "The Grid" – than 1 analysis running at 1 Pflop/s

### **Tutorial M06**

### **Erik P. DeBenedictis**

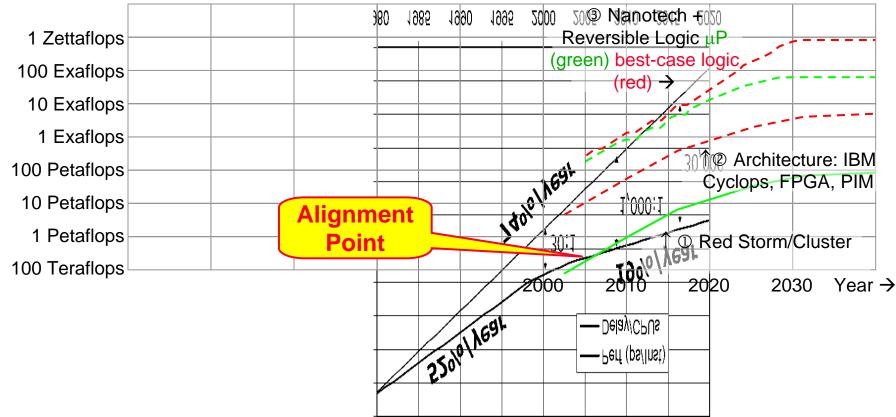

### Outline

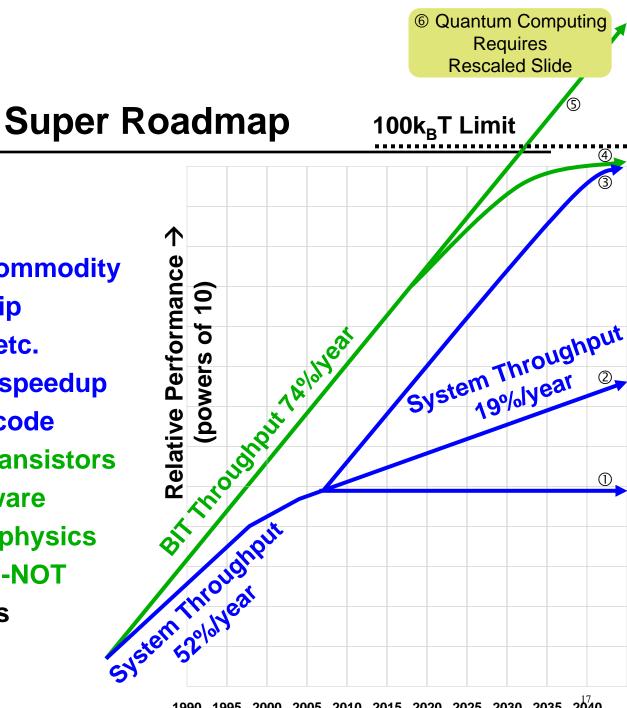

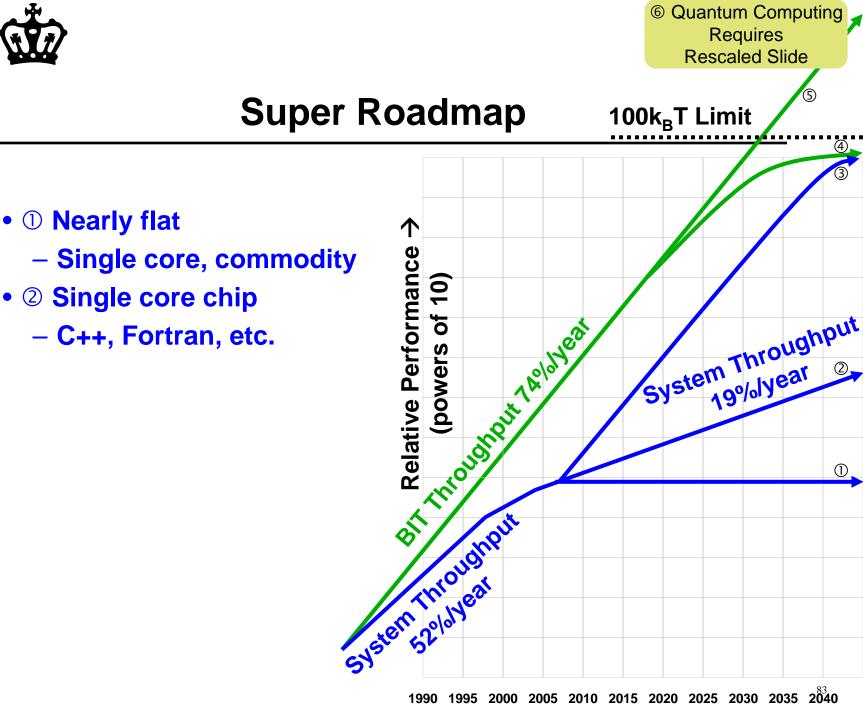

- Overview

- Insight From a Dinner Conversation in DC

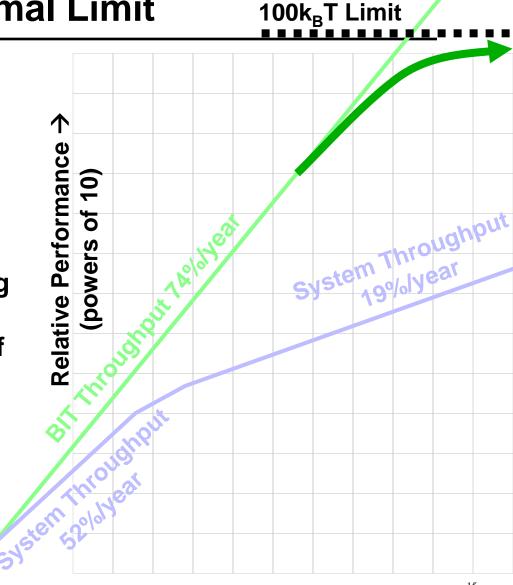

- Super-Roadmap

- Limitations to Moore's Law

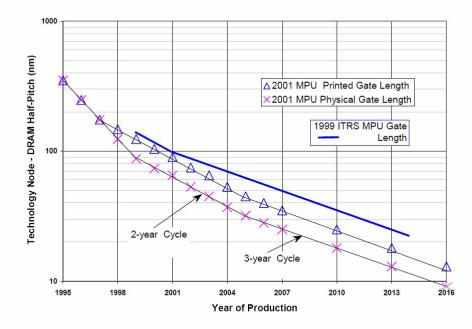

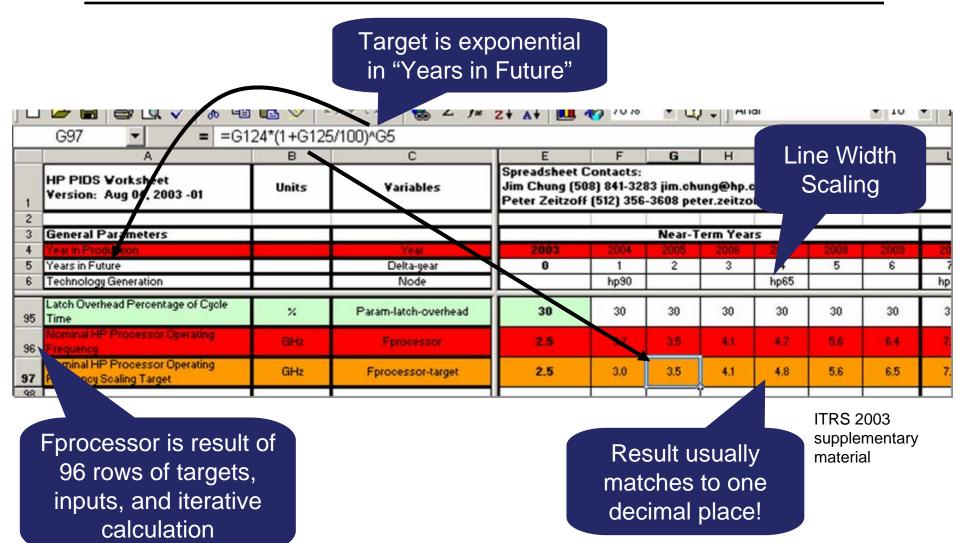

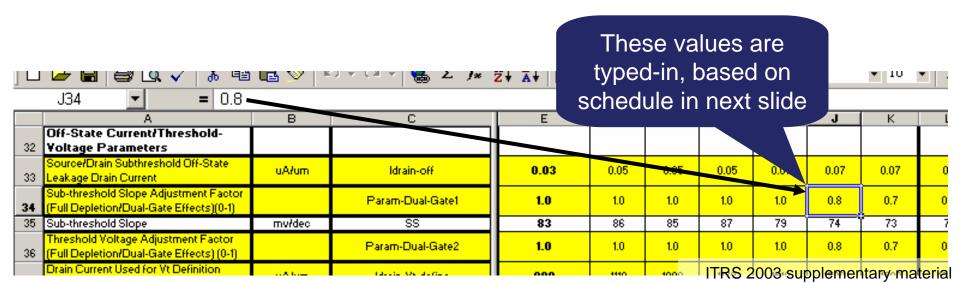

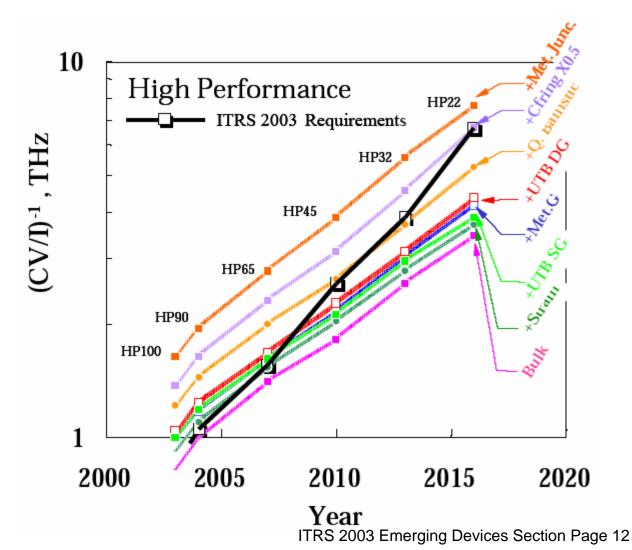

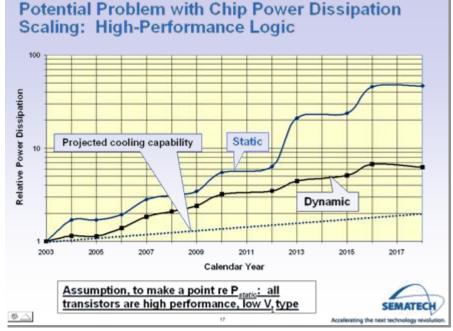

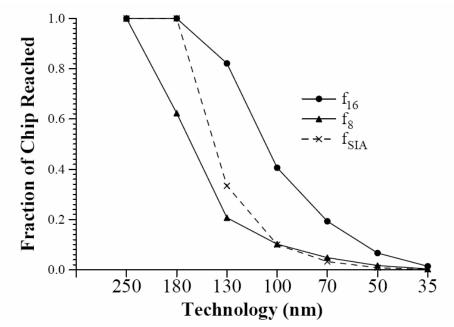

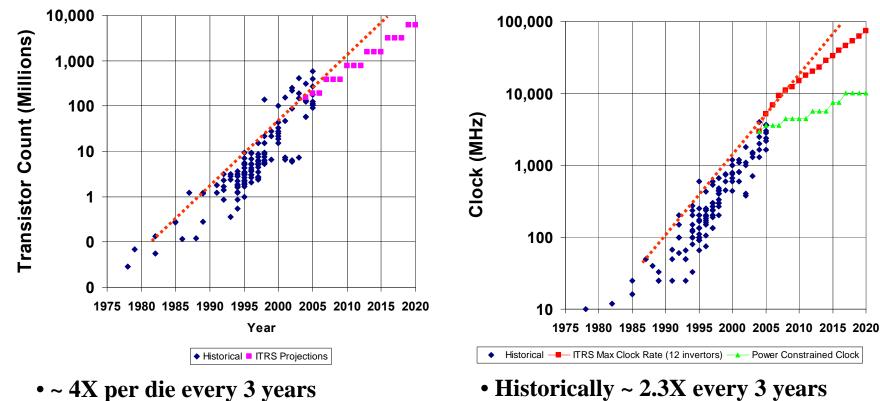

- Transistor Scaling Limits per ITRS

- Consequence to

System Performance

per Burger and Keckler

Study

- What It Means and What To Do About It

- Legacy C++/Fortran

- Systolic Array Lessons

- New Very Parallel Code

- Special Purpose Assist

- Analog/Neural Net

- Over the Horizon

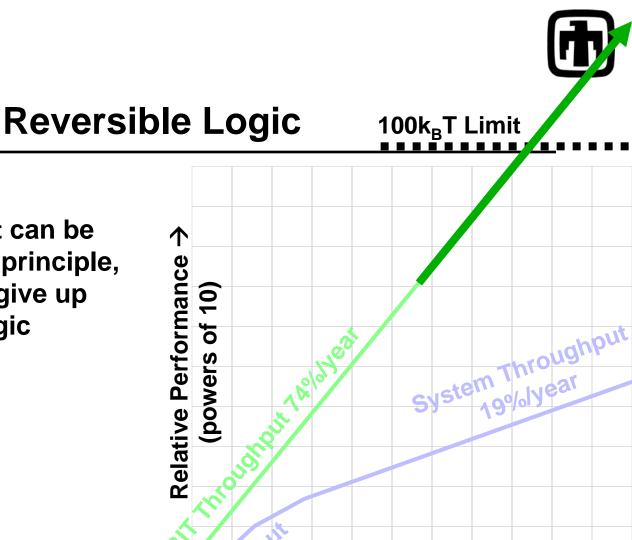

- Reversible Logic

- Quantum Computing

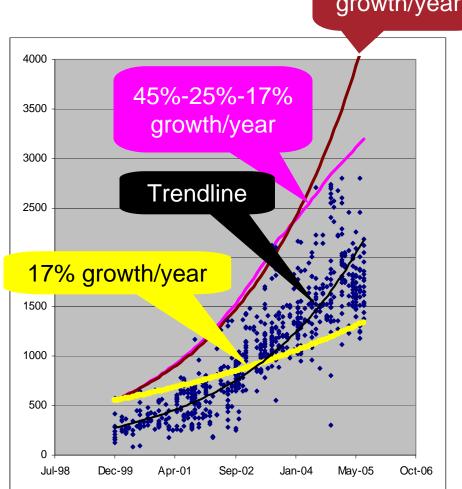

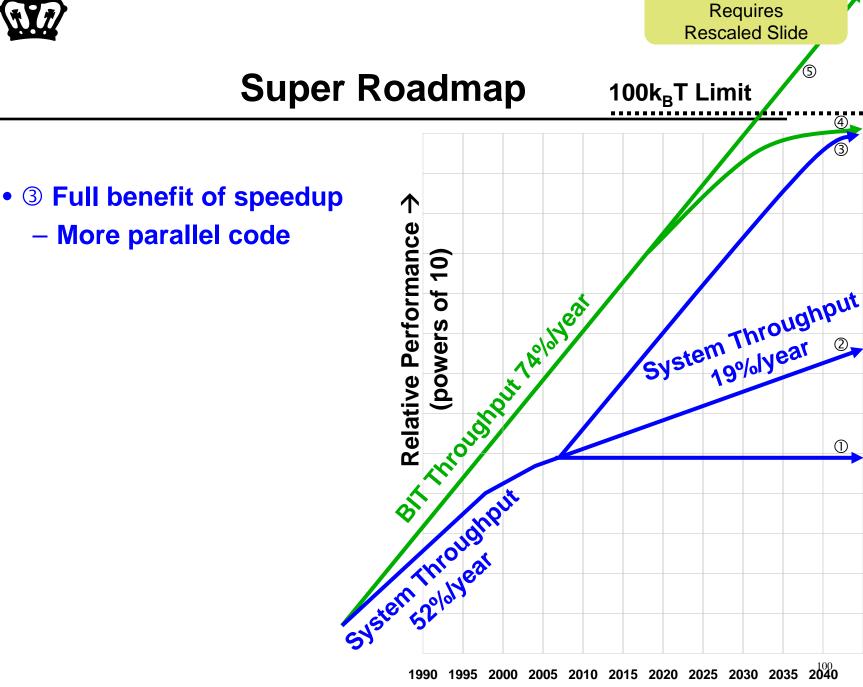

### **Insight From A Dinner Conversation**

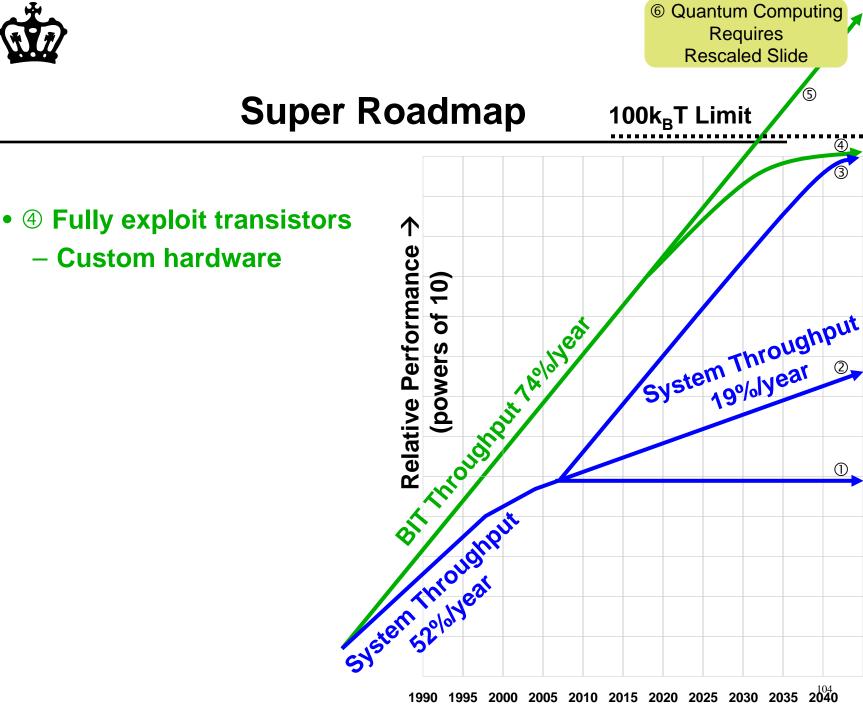

- I have dinner with a physicist at a joint ITRS and electron device meeting in DC 12/2005

- The fellow tells me in hushed tones that he knows the future to Moore's Law

- Is this trivial or profound?

- I ask what it is?

- Answer: More Parallelism.

- I knew this: trivial

- I say there may not be enough parallelism in problems – and has he talked to programmers

- Answer: "no"

- Oh boy, the future of Moore's Law depends on YOU programming smarter and you don't know this: profound

### Outline

- Overview

- Insight From a Dinner

Conversation in DC

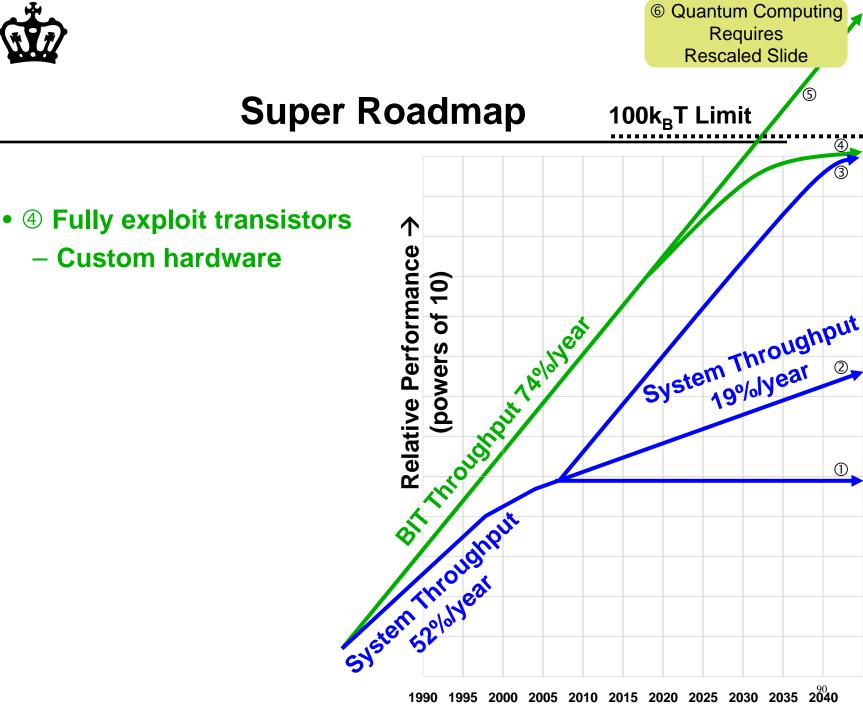

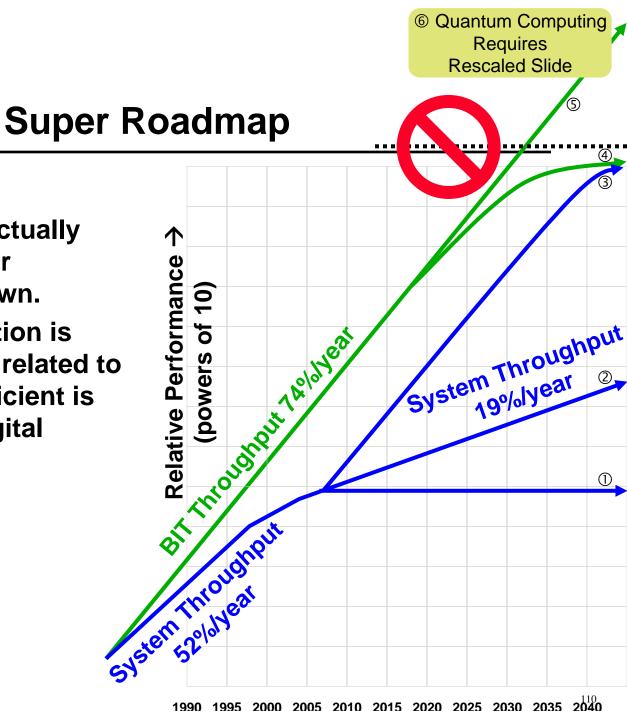

- Super-Roadmap

- Limitations to Moore's Law

- Transistor Scaling Limits per ITRS

- Consequence to

System Performance

per Burger and Keckler

Study

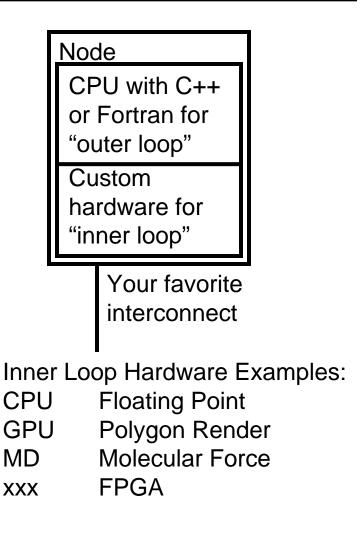

- What It Means and What To Do About It

- Legacy C++/Fortran

- Systolic Array Lessons

- New Very Parallel Code

- Special Purpose Assist

- Analog/Neural Net

- Over the Horizon

- Reversible Logic

- Quantum Computing